# THÈSE

Présentée à L'Ecole Nationale d'Ingénieurs de Tunis

Pour l'obtention du grade de

# DOCTEUR DE L'ECOLE NATIONALE D'INGENIEURS DE TUNIS SPÉCIALITÉ: GÉNIE ÉLECTRIQUE

Pour l'obtention du grade de

# **DOCTEUR DE L'UNIVERSITE DE CERGY-PONTOISE**

Ecole doctorale : Sciences et Ingénierie

Diplôme National - Arrêté du 7 août 2006

SPÉCIALITÉ: GÉNIE ÉLECTRIQUE ET ÉLECTRONIQUE

Présentée par :

Mohamed DAGBAGI

# FPGA-Based Embedded Real Time Simulation of Electrical Systems

Publicly defended on 08 October 2015 in front of the jury composed of:

- President : Prof. Khaled JELASSI, ENIT, Tunisia

- Reviewer : Prof. Ahmed MASMOUDI, ENIS, Tunisia

- Reviewer : Prof. Serge PIERFEDERICI, ENSEM Nancy, France

- Examiner : Prof. François AUGER, Université de Nantes, France

- Advisor : Prof. Eric MONMASSON, Université de Cergy-Pontoise, France

- Advisor : Prof. Ilhem SLAMA-BELKHODJA, ENIT, Tunisia

- Invited : Dr. Lahoucine IDKHAJINE, Université de Cergy-Pontoise, France

This thesis has been performed in the Laboratory of Electrical Systems of ENIT (LR LSE- LR 11 ES 15) and in the SATIE Laboratory of UCP (SATIE - UCP / UMR 8029)

To my parents, To my family, To all those who are dear to me.

# Abstract

The aim of this thesis work is to develop an IP-Library of FPGA-based embedded realtime simulator IPs (Intellectual Properties) that simulate different elements of an electrical system. These IPs have been designed to be used not only for Hardware-In-the-Loop (HIL) testing of digital controllers but also for low cost embedded control applications, where the simulator IP and the controller are both implemented and run altogether in the same FPGA device. This emerging class of real-time simulators is expected to be more and more included in the next generation of digital controllers. Indeed, such embedded real-time simulator IPs can be advantageously embedded within digital controllers to ensure functions like observation, estimation, diagnostic or health-monitoring. Conversely to the HIL case, the main challenge when designing such simulator IPs is to cope with their complexity having in mind that, in the case of embedded systems, the available hardware resources are limited due to the cost. Furthermore, this challenge is strengthened by the need of very short simulation time-steps which is typically the case when simulating power converters.

To develop these IPs, dedicated design guidelines have been proposed to be followed to manage the complexity of these simulator IPs (model solver, numerical solver, time-step, data conditioning) with regards to the timing and the area/cost constraints (computation time limit, limited hardware resources ...).

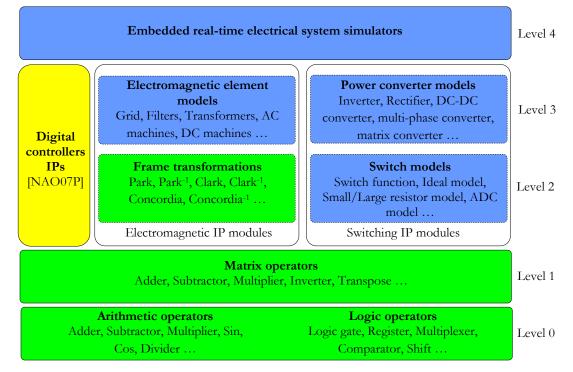

The simulators IPs to be developed have been organized into two main categories: those dedicated to electromagnetic elements of an electrical system and those dedicated to their switching elements.

The first category gathers elements where electric, magnetic phenomena are modelized in addition to mechanical phenomena (for moving systems) and potentially thermal phenomena. Three cases are dealt with: the embedded real-time simulator of a three-phase DC-excited synchronous machine, the one of a three-phase induction machine and the one of a a three-stage avionics alternator. Also, the advantages of using delta transformation to improve the stability of the numerical solver when short simulation time-step and fixed-point (with limited data precision) are used, have been studied.

The second category concerns switching elements such as power converters where switching events are considered. Here again, several converter topologies have been studied: a half-wave rectifier, a buck DC-DC converter, a bidirectional buck DC-DC converter, a H-bridge DC-DC converter, a single-phase H-bridge DC-AC converter, a three-phase voltage source inverter, a three-phase diode rectifier and a three-phase PWM rectifier. For all these IPs, the Associated Discrete Circuit (ADC) modeling approach is adopted.

The embedded real-time simulator IP of the three-phase PWM rectifier has been applied in the context of an embedded application. The latter consists of a fault-tolerant control of a grid-connected voltage source rectifier. Thus, this simulator IP is associated with the one of a three-phase RL-filter and are both implemented within the rectifier controller to estimate the grid currents. These currents are injected in the controller in the case of a current sensor fault. The ability of this estimator to guarantee the service continuity in the case of faults is validated through HIL tests and experiments.

# Keywords

- Field Programmable Gate Array

- Embedded Real-time simulation

- Electrical systems

- Embedded digital controllers

- Hardware In the Loop

- Fault-tolerant control

- Power converters

- AC machines

- Associated Discrete Circuit

- Delta transformation

- Fixed-point data representation

# Résumé

L'objectif de ce travail de thèse est de développer une bibliothèque de modules IPs (Intellectual Properties) de simulateurs temps réel embarqués qui simulent différents éléments d'un système électrique. Ces modules ont été conçus pour être utilisés non seulement pour une validation HIL (Hardware-In-the-Loop) des contrôleurs numériques mais aussi pour des applications de contrôle embarquées, où le module IP de simulateur et le contrôleur sont tous les deux implantés et exécutés dans la même cible FPGA. Cette nouvelle classe de simulateurs temps réel devrait être de plus en plus incluse dans la prochaine génération de contrôleurs numériques. En effet, ces modules IPs de simulateurs temps réel embarqués peuvent être avantageusement intégrés dans les contrôleurs numériques pour assurer des fonctions comme l'observation, l'estimation, le diagnostic où la surveillance de la santé. Inversement aux cas de HIL, le principal défi lors de la conception de tels simulateurs est de faire face à leur complexité ayant à l'esprit que, dans le cas des systèmes embarqués, les ressources matérielles disponibles sont limitées en raison du coût. En outre, ce problème est renforcé par la nécessité des pas de simulation très petits. Ceci est généralement le cas lors de la simulation des convertisseurs de puissance.

Pour développer ces modules IPs, des lignes directrices dédiées de conception ont été proposées pour être suivies pour gérer la complexité de ces simulateurs (solveur de modèle, solveur numérique, pas de simulation, conditionnement de données) tout en tenant compte des contraintes temporelles et matérielles/coût (temps de calcul limité, ressources matérielles limitées ...).

Les modules IPs de simulateurs à développer ont été organisés en deux catégories principales: ceux qui sont consacrées aux éléments électromagnétiques d'un système électrique, et ceux dédiés à ses éléments commutés.

La première catégorie regroupe les éléments électromagnétiques où les phénomènes électriques, magnétiques sont modélisés en plus de phénomènes mécaniques (pour les parties mécaniques) et des phénomènes potentiellement thermiques. Trois cas sont traités: le simulateur temps réel embarqué d'une machine synchrone triphasée, celui d'une machine asynchrone triphasée et celui d'un alternateur avionique à trois étages. En plus de cela, les avantages de l'utilisation de la transformation delta pour améliorer la stabilité du solveur numérique lorsque un petit pas de calcul et le codage virgule fixe (avec une précision de données limitée) sont utilisés, ont été étudiés.

La deuxième catégorie concerne des éléments commutés tels que les convertisseurs de puissance où les événements de commutation sont considérés. Là encore, plusieurs topologies de convertisseurs ont été étudiées: un redresseur simple alternance, un hacheur série, un hacheur réversible en courant, un hacheur quatre quadrant, un onduleur monophasé, un onduleur triphasé, un redresseur à diodes triphasé et un redresseur MLI triphasé. Pour tous ces modules IPs de simulateurs, l'approche de modélisation ADC (Associated Discrete Circuit) est adoptée.

Le module IP de simulateur temps réel embarqué du redresseur MLI a été appliqué dans un contexte d'une application embarquée. Cette dernière consiste en une commande tolérante aux défauts d'un convertisseur de tension coté réseau. Ainsi, ce module IP est associé à celui d'un simulateur temps réel d'un filtre RL triphasé et les deux sont embarqués dans le dispositif de commande du redresseur pour estimer les courants de lignes. Ces courants sont injectés dans le dispositif de cot estimateur de garantir la continuité de service en cas de défauts est validée par des tests HIL et expérimentalement.

# **Mots clefs**

- Réseaux de portes programmables Field Programmable Gate Array

- Simulation temps réel embarquée

- Systèmes électriques

- Commande numérique embarquée

- Procédure Hardware In the Loop

- Commande tolérante aux défauts

- Convertisseurs de puissance

- Machines alternatives

- Associated Discrete Circuit

- Transformée delta

- Codage virgule fixe

# ملخص

الغرض من هذا العمل هو تطوير مكتبة ملكيات فكرية لأجهزة محاكاة مضمنة في الوقت الحقيقي مستندة على FPGA والتي تحاكي مختلف عناصر النظام الكهربائي. هذه الملكيات الفكرية تم تصميمها ليس فقط لاستخدامها في اختبار وحدات التحكم الرقمية بواسطة الأجهزة في الحلقة HIL و لكن أيضا في تطبيقات تحكم مضمنة ومنخفضة التكلفة، حيث جهاز المحاكاة و وحدة التحكم كلاهما يوجدان ويشتغلان داخل نفس الجذاذة الرقمية FPGA. هذه الفئة الناشئة من أجهزة المحاكاة في الوقت الحقيقي من المتوقع أن تكون أكثر فأكثر مدرجة في الجيل القادم من وحدات التحكم الرقمية. في الواقع، مثل في الوقت الحقيقي من المتوقع أن تكون أكثر فأكثر مدرجة في الجيل القادم من وحدات التحكم الرقمية. في الواقع، مثل أجهزة المحاكاة المضمنة في الوقت الحقيقي هذه يمكن أن تكون جزأ لا يتجزأ مفيد في وحدات التحكم الرقمية لضمان وظائف مثل الملاحظة والتقدير والتشخيص أو رصد الصحة. على عكس حالة الإختبار بواسطة HIL، فإن التحدي الرئيسي عند تصميم مثل أجهزة المحاكاة هذه هو التعامل مع تعقيداتها مع الأخذ في الاعتبار أنه في حالة المضمنة، موارد الأجهزة المتاحة محدودة بسبب التكلفة. علاوة على ذلك، تم تعزيز هذا التحدي من خلال الخرية موارد الأجهزة المتاحة محدودة بسبب التكلفة. علاوة على ذلك، تم تعزيز هذا التحدي من خلال المحاكاة وقت قصيرة جدا، وهذا هو الحال عادة عند محاكاة محولات الطاقة.

لتطوير هذه الملكيات الفكرية، تم اقتراح إرشادات تصميم مخصص, الواجب اتباعها لإدارة تعقيد هذه المحاكاة (حَلّال النموذج ، الحَلَّال العددي، خطوة الوقت ، تكبيف البيانات) بنظر إلي القيود المتعلقة بالتوقيت و المنطقة / التكلفة (الحد الزمني لحساب، موارد الأجهزة محدودة ...).

المحاكاة التي سيتم تطوير ها نظمت إلى فئتين رئيسيتين: تلك المخصصة للعناصر الكهر ومغناطيسية للنظام الكهربائي وتلك المخصصة لعناصر التحويل الخاصة به.

الفئة الأولى تجمع عناصر حيث وضعت نماذج للظواهر الكهربائية والمغناطيسية بالإضافة إلى الظواهر الميكانيكية (أنظمة التحرك) والظواهر يحتمل الحرارية. تم تناول ثلاث حالات: جهاز محاكاة مضمن في الوقت الحقيقي لآلة تزامنية ثلاثية الاطوار، واحد لألة غير تزامنية ثلاثية الاطوار و واحد لمولد إلكترونيات الطيران ثلاث مراحل. أيضا، فإنه تمت دراسة مزايا استخدام التحول دلتا لتحسين استقرار الحَلَّل العددي عندما تستخدم المحاكاة قصيرة خطوة الوقت ونقطة ثابتة لتمثيل البيانات (مع دقة بيانات محدودة).

الفئة الثانية تهتم بعناصر التحويل مثل محولات الطاقة أين أحداث التحويل مأخوذة بعين الأعتبار. هنا مرة أخرى، تمت دراسة عدة مخططات تحويل: مقوم نصف الموجة، محول باك، محول باك ثنائي الاتجاه، محول مستمر متردد أربعة رباعي، محول جهد ثلاثي الاطوار، مقوم بديودات ثلاثي الاطوار, مقوم تظمين عرض النبظة ثلاثي الاطوار. لجميع أجهزة المحاكاة هذه اعتمدت تقنية نهج النماذج ADC.

جهاز محاكاة المظمن في الوقت الحقيقي لمقوم تظمين عرض النبظة ثلاثي الاطوار تم إستعماله في سياق تطبيق المضمنة. يتكون هذا الأخير من عنصر تحكم في مقوم مصدر الجهد متصل بالشبكة قادر على استيعاب الأخطاء. وهكذا، فإن جهاز المحاكاة هذا تم ربطه بجهاز محاكاة أخر لفلتر RL ثلاثي الاطوار وكلاهما تم دمجهما ضمن وحدة التحكم في المقوم لتقدير تيارات الشبكة. يتم حقن هذه التيارات في وحدة التحكم في حالة وجود خطأ في حساس التيار. قدرة هذا المقدر لضمان استمرارية الخدمة في حالة الاعطال تم التحقق من صحتها من خلال اختبارات إلا والتجارب.

# كلمات مفاتيح

- شرائح مصفوفة البوابات المنطقية القابلة للبرمجة

- محاكاة مضمنة في الوقت الحقيقي

- الأنظمة الكهربائية

- التحكم الرقمي المضمن

- إجراء الأجهزة في حلقة

- التحكم المتسامح مع الأخطأ

- محولات الطاقة

- ألات تيار متردد

- الدائرة الغير مستمرة المرتبطة

- تحول دلتا

- ترميز النقطة الثابتة

# Acknowledgments

The work presented in this thesis has been carried out in the context of a joint PhD dissertation through a joint supervision between two research laboratories: The "Laboratoire des Systèmes Electriques (LSE)" of "Ecole Nationale d'Ingénieurs de Tunis (ENIT)" and the "Laboratoire des Systèmes et Applications des Technologies de l'Information et de l'Energie (SATIE), antenne de l'Université de Cergy-Pontoise (UCP)".

These few acknowledgments reflect my gratitude for all those who have contributed directly or indirectly to the success of this work.

In the first place, I would like to express my profound gratitude to Professor. Eric MONMASSON, my advisor, and Head of the "Laboratoire SATIE, antenne de l'UCP", for supervising my thesis work, his valuable guidance and providing an excellent research environment during my stay in France.

I which to express my gratitude to Professor Ms. Ilhem SLAMA-BELKHODJA, my advisor and Head of "Laboratoire LSE, à l'ENIT", for supervising my thesis work, for her confidence and her encouragements.

I would like to strongly thank Mr. Lahoucine IDKHAJINE, Associate Professor in UCP and member of "Laboratoire SATIE", for his patience and generosity devoted valuable time and provided great help to the development of this work.

Also, I thank Professors Khaled JELASSI, Ahmed MASMOUDI, Serge PIERFEDERICI and François AUGER for reviewing and examining this thesis work.

I also take this opportunity to express my deep gratitude to Marie-Hélène MOREAU, Aude BREBANT and Don Abasse BOUKARI for making my stay in France easy by taking care of all the administrative aspects and the small daily worries.

I which also to thank all my family members, especially my loving mother Rebeh and my dear father Hassen, for their encouragements and support during the past years.

Many thanks also to all my laboratory friends in "Laboratoire LSE" and "Laboratoire SATIE" for their friendships and for the scientific discussions along with the common friendly banters that we always enjoy.

Finaly, I would like to thank my past and recent institutes "Institut Supérieur d'Informatique - (ISI)" and "ENIT" for making this possible.

DAGBAGI Mohamed

# Contents

| Abstrac    | t                                                                     | I   |

|------------|-----------------------------------------------------------------------|-----|

| Keywor     | ds                                                                    | Π   |

| Résumé     |                                                                       | Ш   |

| Mots cle   | fs                                                                    | IV  |

|            |                                                                       |     |

| مات مفاتيح | كل.                                                                   | VI  |

| Acknow     | ledgmentsV                                                            | /II |

| Content    | sV                                                                    | III |

| General    | Introduction                                                          | .1  |

|            | sis objectives and author contributions                               |     |

| 2. The     | sis outline                                                           | .4  |

| 3. Non     | nenclature                                                            | . 5 |

| 3.1.       | Symbols                                                               | . 5 |

| 3.2.       | Indexes                                                               |     |

| 3.3.       | Abbreviations                                                         |     |

| -          | 1: State of the art real-time simulation of electrical systems        |     |

|            | oduction                                                              |     |

|            | ine vs real-time simulation                                           |     |

| 2.1.       | Offline simulation                                                    |     |

| 2.2.       | Real-time simulation                                                  |     |

|            | l-time digital simulation of electrical systems - Applications trends |     |

| 3.1.       | Controller HIL simulation                                             |     |

| 3.2.       | Power HIL simulation                                                  |     |

|            | leling and representation of electrical systems                       |     |

| 4.1.       | Model solvers                                                         |     |

| <i>a</i> - | State-space solver                                                    |     |

| <i>b</i> - | Nodal solver                                                          |     |

| 4.2.       | Modeling of switching elements                                        |     |

| <i>a</i> - | Modeling at the system scale                                          |     |

|            | Switching function modeling                                           |     |

| L          |                                                                       |     |

| <i>b</i> - | Modeling at the switch scale                                          |     |

|            | Physical modeling                                                     |     |

|            | Behavioral modeling<br>Two-valued switch modeling                     |     |

|            | - Small/large resistor model                                          |     |

|            | <ul> <li>ADC-based model</li></ul>                                    |     |

| 4.3.       | Modeling of electromagnetic elements                                  |     |

| a-         | Natural phase-domain model                                            |     |

| и<br>b-    | Bi-phase model                                                        |     |

|            | tal realization                                                       |     |

| 5.1.       | Numerical solvers                                                     |     |

| з.н.<br>а- | Explicit methods                                                      |     |

| и<br>b-    | Implicit methods                                                      |     |

| 5.2.       | Simulation time-step selection                                        |     |

| a-         | Time-step vs system dynamics                                          |     |

| <i>b</i> - | <i>Time-step vs interfacing errors</i>                                |     |

| С-         | <i>Time-step vs numerical stability</i>                               |     |

|            | · ·                                                                   |     |

| d-         | Time-step vs real-time operation                                                                                     | 25 |

|------------|----------------------------------------------------------------------------------------------------------------------|----|

| 5.3.       |                                                                                                                      |    |

| 6. Dig     | gital implementation                                                                                                 |    |

| 6.1.       | Evolution of real-time digital simulation technologies                                                               | 26 |

| 6.2.       |                                                                                                                      |    |

| 7. Co      | nclusion                                                                                                             |    |

| Chapte     | r 2: FPGA-based embedded real-time simulation of electrical systems                                                  | 31 |

| 1. Inti    | roduction                                                                                                            | 32 |

| 2. FP      | GA-based embedded real-time simulation                                                                               | 32 |

| 2.1.       | Embedded real-time simulation                                                                                        | 32 |

| 2.2.       | Use of FPGAs                                                                                                         | 35 |

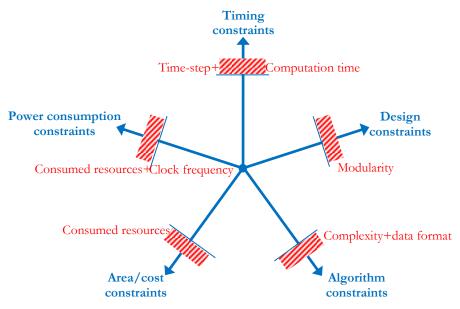

| 3. FP      | GA-based embedded real-time simulation constraints                                                                   | 36 |

| 3.1.       | Timing constraints                                                                                                   |    |

| 3.2.       | Design constraints (modularity)                                                                                      | 36 |

| 3.3.       | Algorithm constraints                                                                                                |    |

| 3.4.       | Area/Cost constraints                                                                                                |    |

| 3.5.       | Power consumption constraints                                                                                        | 38 |

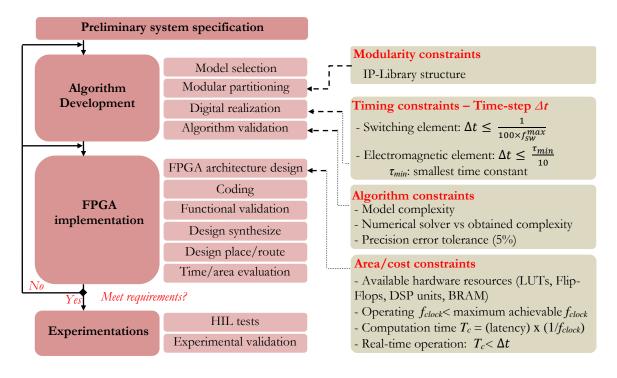

|            | sign guidelines for developing FPGA-based embedded real time simulators                                              |    |

| 4.1.       | Preliminary system specification                                                                                     | 39 |

| 4.2.       | Algorithm development                                                                                                |    |

| 4.3.       | FPGA Implementation                                                                                                  |    |

| 4.4.       | Experimentations                                                                                                     |    |

|            | nclusion                                                                                                             |    |

| _          | r 3: Implementation in low cost FPGA of embedded real-time simulator IPs                                             |    |

|            | magnetic elements                                                                                                    |    |

|            | roduction                                                                                                            | 44 |

|            | GA-based embedded real-time simulator of a 3-phase DC-excited synchronous                                            |    |

|            |                                                                                                                      |    |

| 2.1.       | Preliminary system specification                                                                                     |    |

| 2.2.       | Algorithm development                                                                                                |    |

| a-         | Model selection                                                                                                      |    |

| <i>b</i> - | Modular partitioning                                                                                                 |    |

| С-         | Digital realization                                                                                                  |    |

| L          | <ul> <li>Digital realization based on shift-operator</li> <li>Digital realization based on dalta operator</li> </ul> |    |

|            | Digital realization based on delta-operator                                                                          |    |

| d-         | Comparative study                                                                                                    |    |

| 2.3.       | FPGA implementation                                                                                                  |    |

|            | FPGA architecture design                                                                                             |    |

| а-<br>b-   | Coding                                                                                                               |    |

| 0-<br>C-   | Functional validation                                                                                                |    |

| d-         | Design/synthesis/place/route                                                                                         |    |

| а<br>е-    | Time/Area evaluation                                                                                                 |    |

| 2.4.       | Experimentations                                                                                                     |    |

| 2.1.<br>a- | HIL tests                                                                                                            |    |

|            | GA-based embedded real-time simulator of a 3-phase induction machine                                                 |    |

|            | GA-based embedded real-time simulator of a three-stage avionics alternator                                           |    |

|            | nclusion                                                                                                             |    |

|            | r 4: Implementation in low cost FPGA of embedded real-time simulator IPs                                             |    |

| -          | ng elements                                                                                                          |    |

|            |                                                                                                                      |    |

|      | Introduction<br>FPGA-based embedded real-time simulator IP of a single-phase DC-AC power conv |       |

|------|-----------------------------------------------------------------------------------------------|-------|

|      | 73                                                                                            | CITCI |

| 2.1  |                                                                                               | 73    |

| 2.1  | 5 5 1                                                                                         |       |

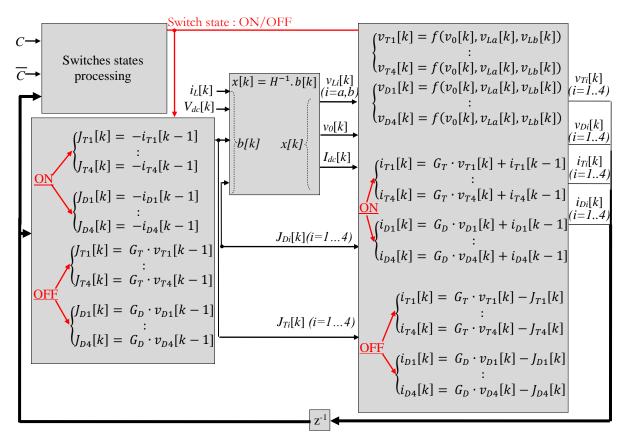

|      | a- Model selection                                                                            |       |

|      | b- Modular partitioning                                                                       |       |

|      |                                                                                               |       |

|      | c- Digital realization<br>l- Algorithm validation                                             |       |

|      | 6                                                                                             |       |

| 2.3  | 1                                                                                             |       |

|      | a- FPGA architecture design                                                                   |       |

|      | b- Coding & Functional validation                                                             |       |

|      | c- Design/synthesis/place/route and Time/Area evaluation                                      |       |

| 2.4  | 1                                                                                             |       |

|      | a- HIL tests                                                                                  |       |

|      | FPGA-based embedded real-time simulator IP of a 3-phase voltage source inverter               |       |

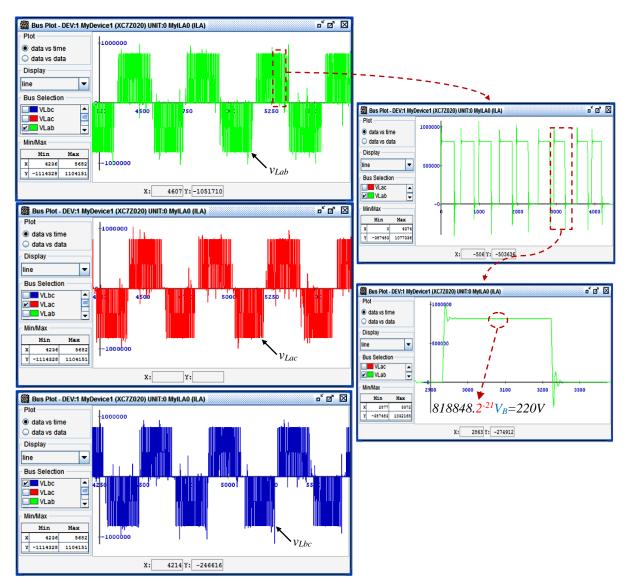

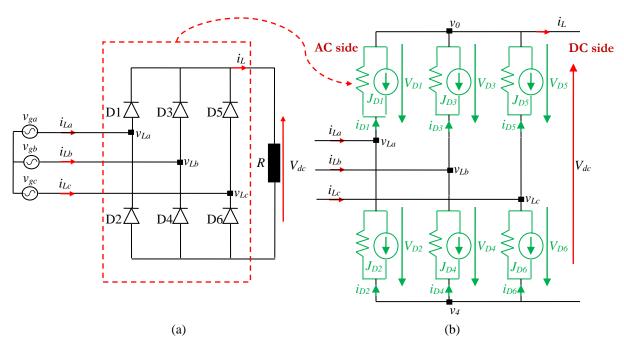

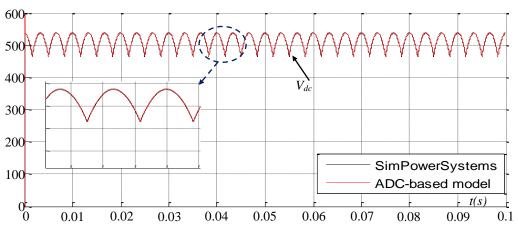

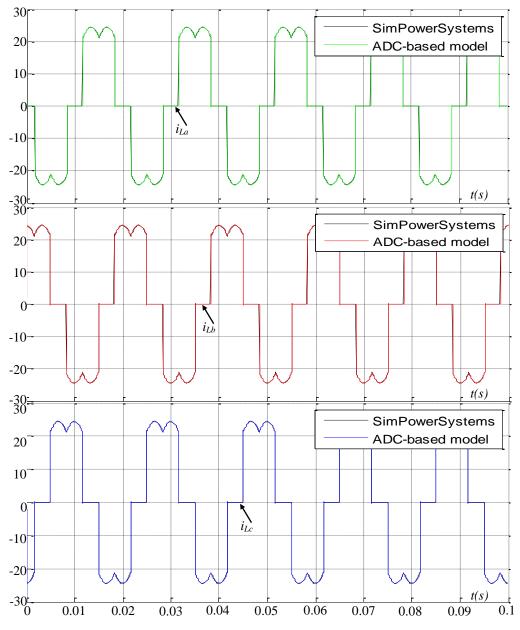

|      | FPGA-based embedded real-time simulator IP of a 3-phase diode rectifier                       |       |

|      | Conclusion                                                                                    |       |

| -    | pter 5: Embedded Real-Time Simulator IPs of PWM Rectifier and 3-phase                         |       |

|      | r: Application to a Fault-Tolerant Control of a Grid-Connected Voltage So                     |       |

| Rect | ifier                                                                                         | 92    |

| 1. ] | Introduction                                                                                  | 93    |

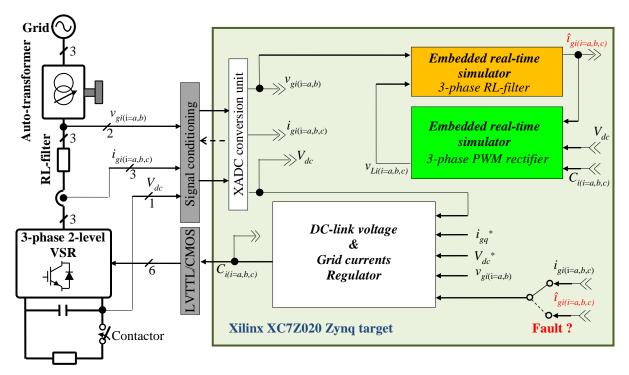

| 2. l | Preliminary system specification                                                              | 93    |

| 2.1  | . DC-link voltage and grid currents regulator                                                 | 94    |

| 2.2  | 2. XADC conversion unit                                                                       | 95    |

| 3.   | Algorithm development                                                                         | 96    |

| 3.1  | Algorithm of the PWM rectifier simulator                                                      | 96    |

| 3.2  | 2. Algorithm of the 3-phase RL-filter simulator                                               | 98    |

| 4. ] | FPGA implementation                                                                           |       |

| 4.1  | 1                                                                                             |       |

| (    | a- Architecture of the PWM rectifier simulator                                                |       |

|      | b- Architecture of the 3-phase RL-filter simulator                                            |       |

| 4.2  |                                                                                               |       |

|      | Experimentations                                                                              |       |

| 5.1  |                                                                                               |       |

| 5.2  |                                                                                               |       |

|      | Conclusion                                                                                    |       |

|      | eral conclusion and perspectives                                                              |       |

|      |                                                                                               |       |

|      | General conclusion                                                                            |       |

|      | Perspectives                                                                                  |       |

| App  | endix A: Current-voltage relations of an ADC equivalent circuit                               | .114  |

| App  | endix B: Parameters of the delta-operator based synchronous machine model                     | 118   |

|      | endix C: Poles of the delta-operator based synchronous machine model                          |       |

| App  | endix D: Parameters of the induction machine                                                  | 123   |

| Ann  | endix E: Components of the three-stage avionics alternator                                    | 125   |

|      | Main generator                                                                                |       |

|      | Nominal load                                                                                  |       |

|      | Exciter Machine                                                                               |       |

| J. 1 |                                                                                               | 120   |

| App | pendix F: IPs modules of the 1-phase AC load and P+Resonant current controlle | er.129 |

|-----|-------------------------------------------------------------------------------|--------|

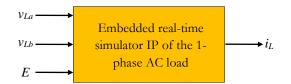

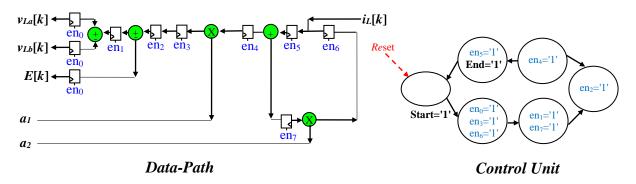

| 1.  | Embedded real-time simulator IP of the 1-phase AC load                        | 130    |

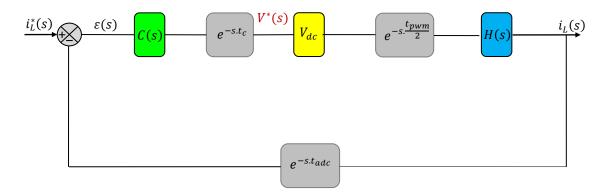

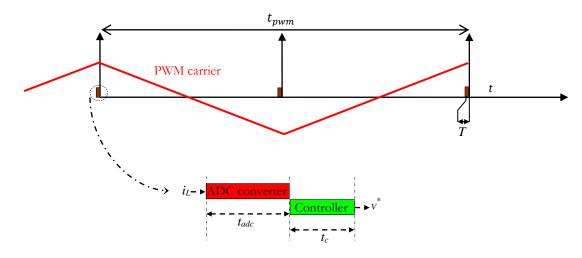

| 2.  | AC Load current controller                                                    | 130    |

| Bib | liography                                                                     | 133    |

# **List of Figures**

# Chapter 1:

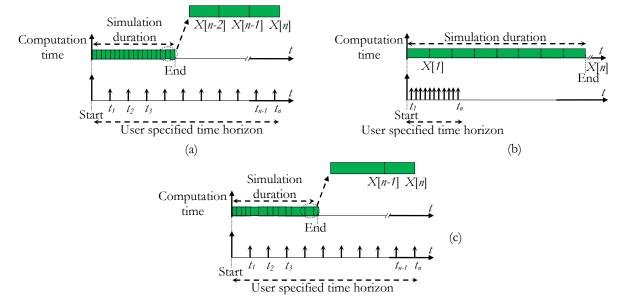

| Figure 1. 1: Offline simulation – (a) Fixed-step simulation - duration shorter than the tim          | е     |

|------------------------------------------------------------------------------------------------------|-------|

| horizon; (b) Fixed step simulation - duration longer than the time horizon; (c) Variable-su          | tep   |

| simulation                                                                                           | 9     |

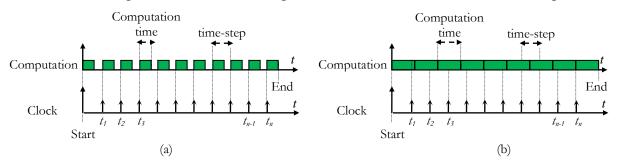

| Figure 1. 2: Real-time simulation cases. (a) Real-time operation; (b) Overruns                       | 10    |

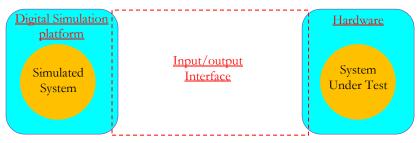

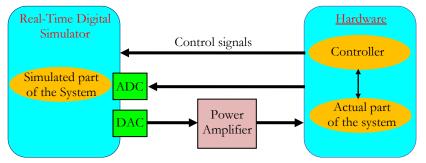

| Figure 1. 3: General structure of a HIL simulation                                                   | 10    |

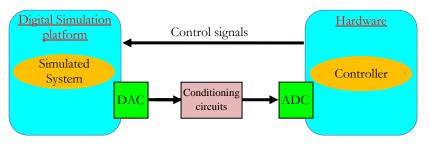

| Figure 1. 4: Structure of a CHIL simulation                                                          | 11    |

| Figure 1. 5: Structure of a PHIL simulation                                                          | 11    |

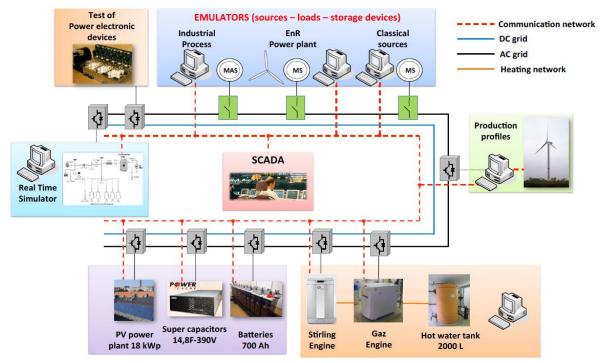

| Figure 1. 6: Distributed Energy Lab - Source: [L2EP]                                                 | 12    |

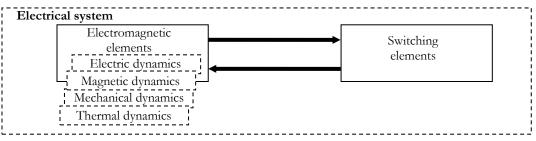

| Figure 1. 7: Components of an electrical system                                                      | 12    |

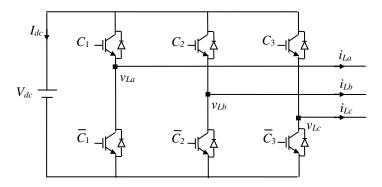

| Figure 1. 8: Circuit diagram of a 3-phase inverter                                                   | 15    |

| Figure 1. 9: Functional block diagram of one 3-level voltage source converter leg, extract           | ted   |

| from [MAY11]                                                                                         | 17    |

| Figure 1. 10: Small/large resistor representation                                                    | 18    |

| Figure 1. 11: Principal of ADC-based model                                                           |       |

| Figure 1. 12: Bi-phase model (a) Model in fixed frame $(\alpha,\beta)$ (b) Model in rotating frame ( | (d,q) |

|                                                                                                      |       |

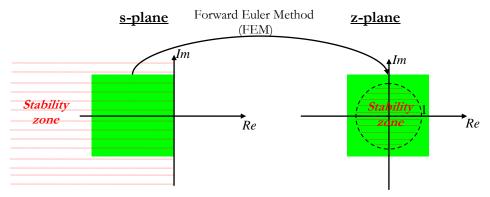

| Figure 1. 13: Stability of the Forward Euler Method                                                  |       |

| Figure 1. 14: Stability of the Implicit Trapezoidal Method                                           | 22    |

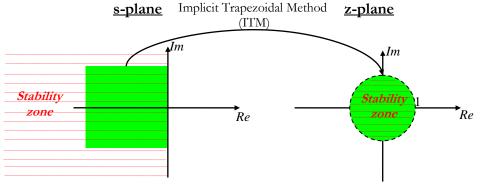

| Figure 1. 15: (a) DC-DC converter circuit after switching (b) its equivalent ADC-based               |       |

| circuit                                                                                              | 22    |

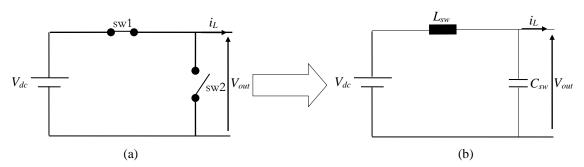

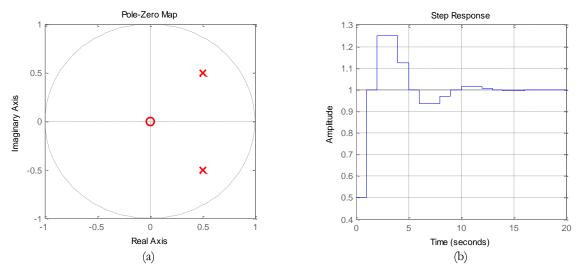

| Figure 1. 16: Results when the ITM is used (a) Location of the poles and zeros in the z-pla          | ane   |

| (b) Step response                                                                                    | 23    |

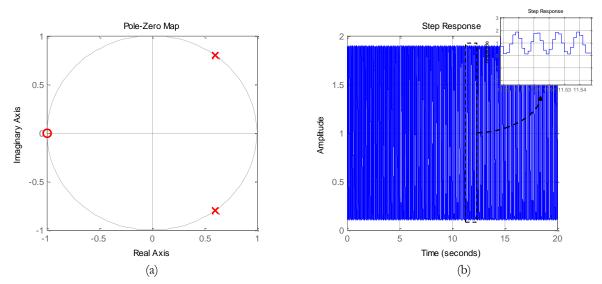

| Figure 1. 17: Results when the BEM is used (a) Location of the poles and zeros in the z-pl           |       |

| (b) Step response                                                                                    |       |

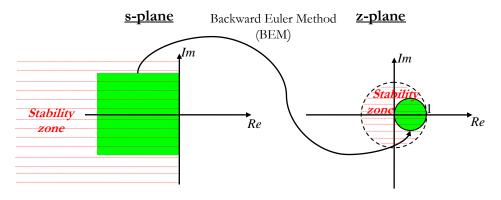

| Figure 1. 18: Stability of the Backward Euler Method                                                 |       |

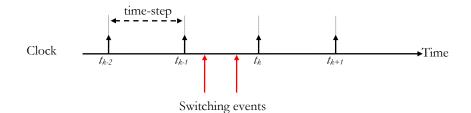

| Figure 1. 19: Inter simulation time-step issue                                                       |       |

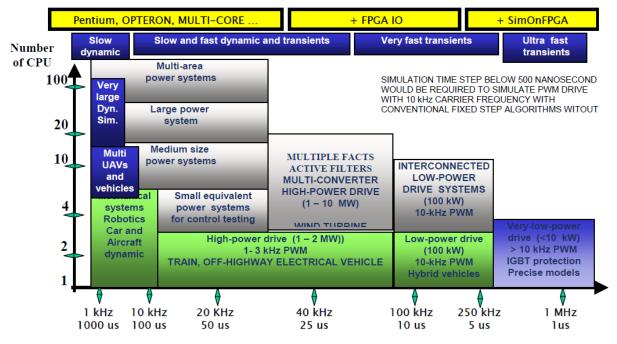

| Figure 1. 20: Simulation time-step vs number of processors, extracted from [BEL07]                   |       |

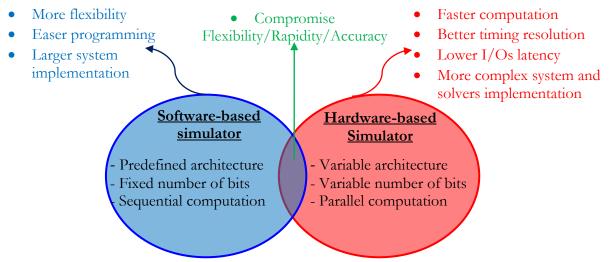

| Figure 1. 21: Software-based and hardware-based simulations                                          | 28    |

|                                                                                                      |       |

# Chapter 2:

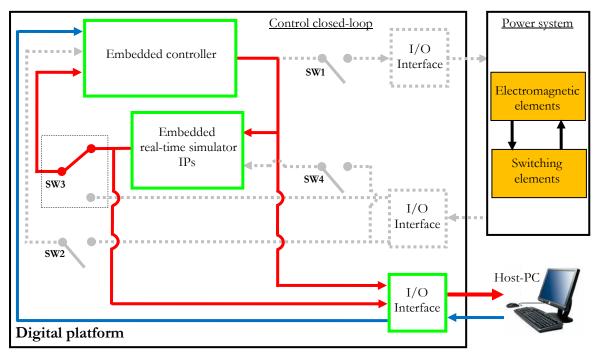

| <i>Figure 2.1: Embedded real-time simulator IPs applied in the context of HIL validation</i> | 33 |

|----------------------------------------------------------------------------------------------|----|

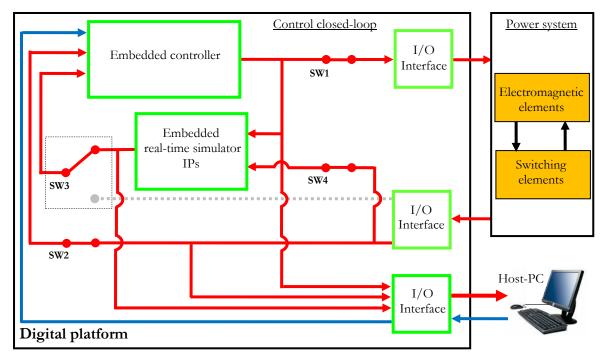

| Figure 2.2: Embedded real-time simulator IPs included inside the control closed-loop and     |    |

| applied in the context of sensorless control                                                 | 33 |

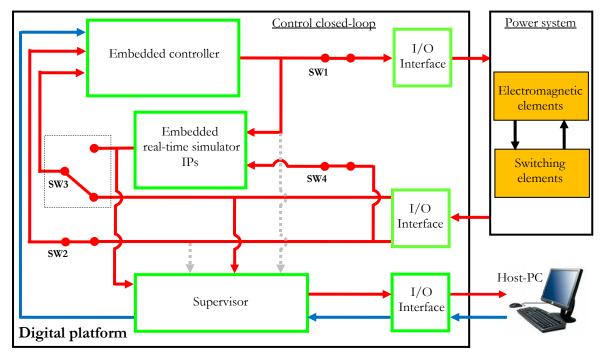

| Figure 2.3: Embedded real-time simulator IPs included inside the control closed-loop and     |    |

| applied in the context of fault-tolerant control                                             | 34 |

| Figure 2.4: Embedded real-time simulator IPs parallelized with the controller and applied i  | n  |

| the context of diagnostic and health-monitoring                                              | 34 |

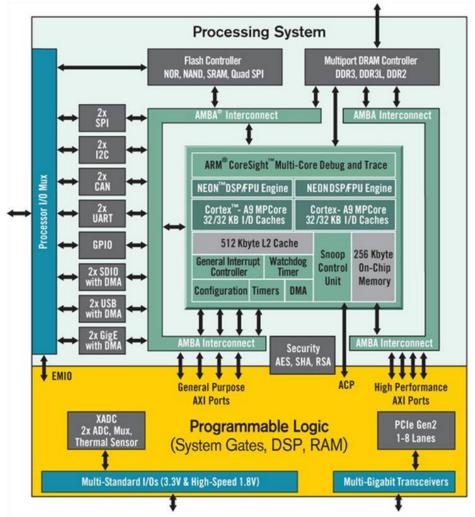

| Figure 2.5: Example of FPGA SoC internal structure: Zynq-7000 device (source: [XIL])         | 35 |

| Figure 2.6: FPGA-based embedded real-time simulation constraints                             | 36 |

| Figure 2.7: IP-Library for FPGA-based embedded real-time simulators                          | 37 |

| Figure 2.8: Design guidelines for FPGA-based embedded real-time simulators                   | 39 |

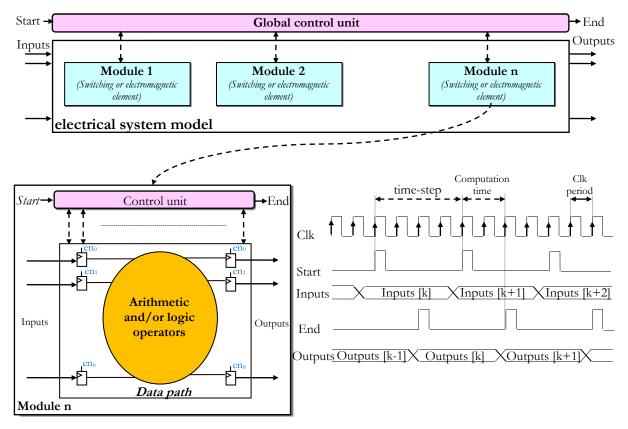

| Figure 2.9: Proposed structure of an | FPGA-based architecture of | an electrical system model |

|--------------------------------------|----------------------------|----------------------------|

|                                      |                            |                            |

# Chapter 3:

| -                                                                                                                                                                                                    |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

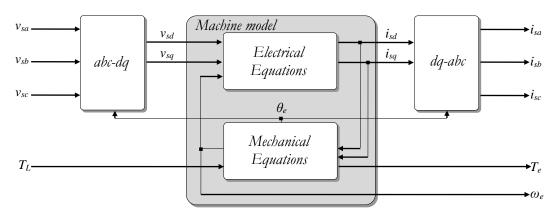

| Figure 3.1: d-q based synchronous machine model - modular partitioning                                                                                                                               | 46 |

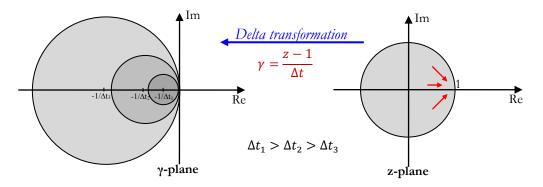

| Figure 3.2: Stability regions of z-domain and $\gamma$ -domain with regards to the time-step $\Delta t$                                                                                              |    |

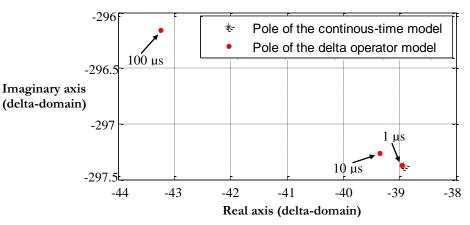

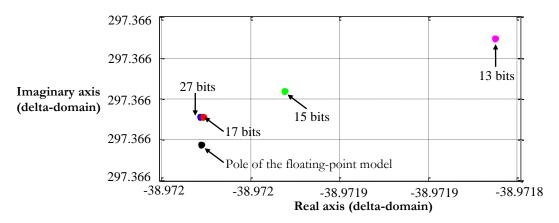

| Figure 3.3: Location of delta-operator model poles depending on the time-step                                                                                                                        |    |

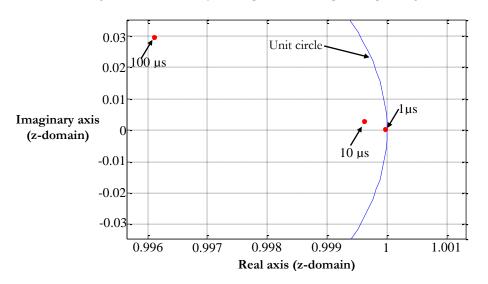

| Figure 3.4: Location of shift-operator model poles depending on the time-step                                                                                                                        |    |

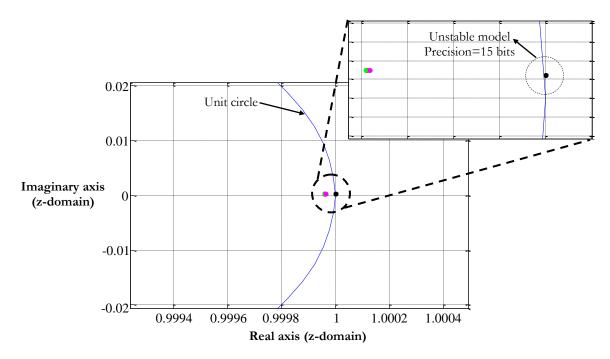

| Figure 3.5: Impact of the fixed-point format on the stability of shift-operator model                                                                                                                |    |

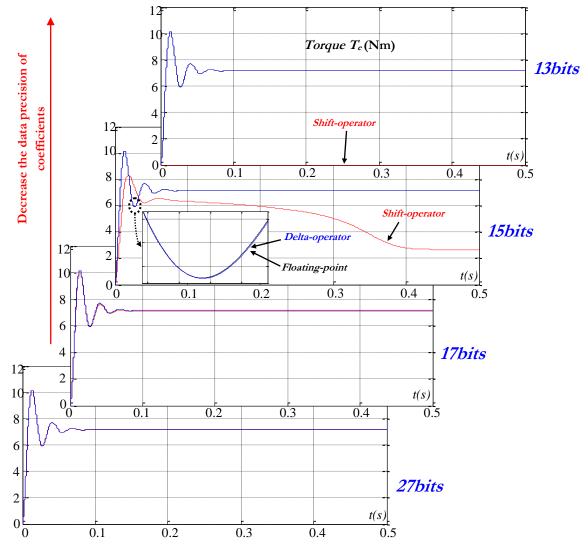

| Figure 3.6: Influence of the data fixed-point precision on the torque response                                                                                                                       |    |

| Figure 3.7: Impact of the fixed-point format on the stability of delta-operator model                                                                                                                |    |

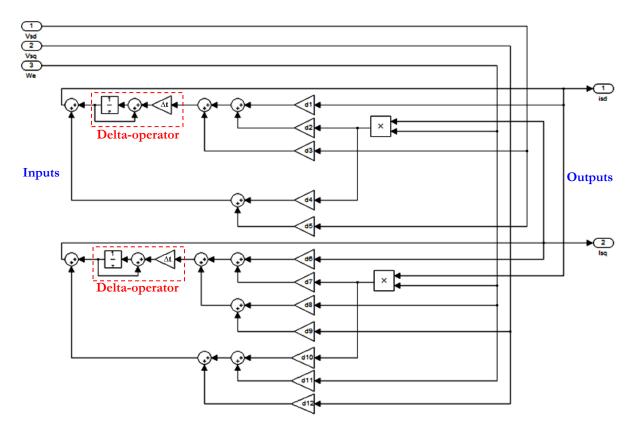

| Figure 3.8: Structure of the delta operator based electrical equations                                                                                                                               |    |

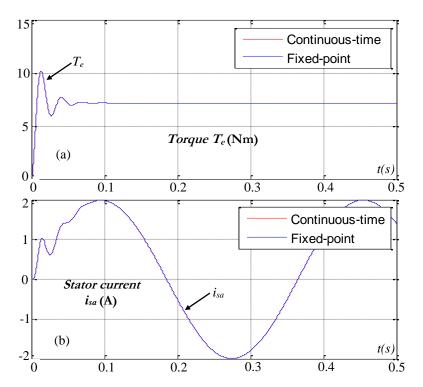

| Figure 3.9: Open-loop simulation results: (a) electromagnetic torque $T_e$ and (b) stator                                                                                                            |    |

| current i <sub>sa</sub>                                                                                                                                                                              | 52 |

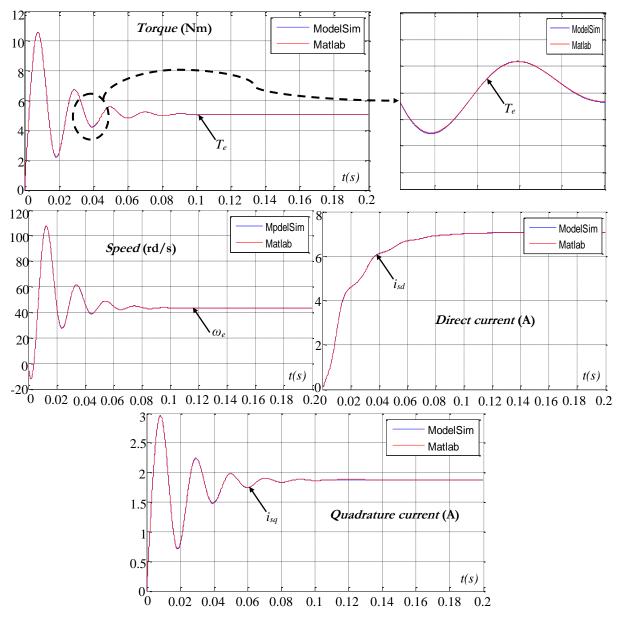

| Figure 3.10: Closed-loop simulations results (a) electromagnetic torque $T_e$ (b) stator cu                                                                                                          |    |

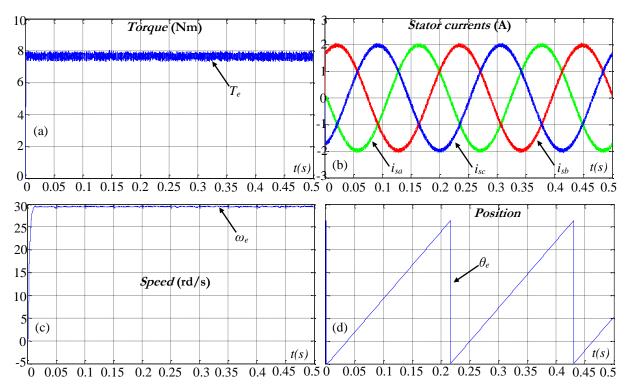

| $i_{si \ (i=a,b,c)}$ (c) speed $\omega_e$ (d) position $\theta_e$                                                                                                                                    |    |

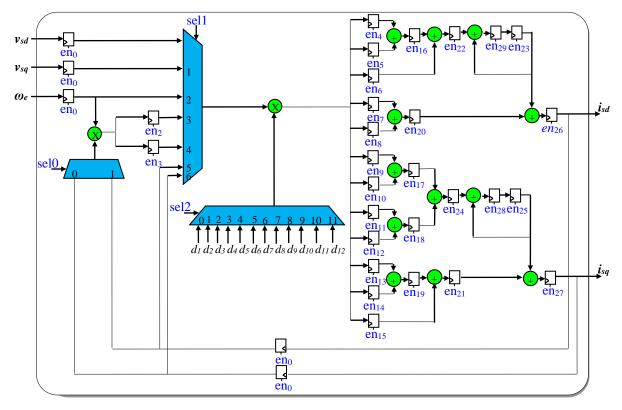

| Figure 3.11: Architecture of delta-operator based synchronous machine real-time simul                                                                                                                |    |

| electrical module                                                                                                                                                                                    |    |

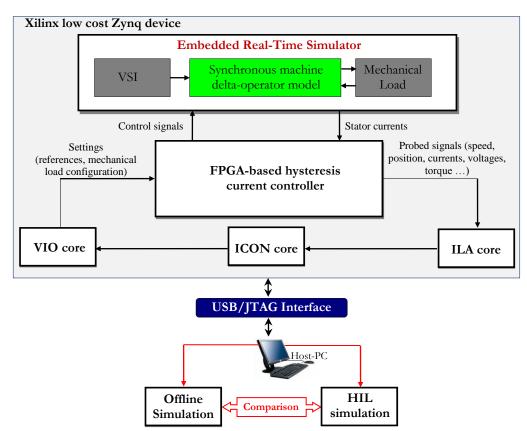

| Figure 3.12: Comparison between Simulink continuous-time simulation results and Mod                                                                                                                  |    |

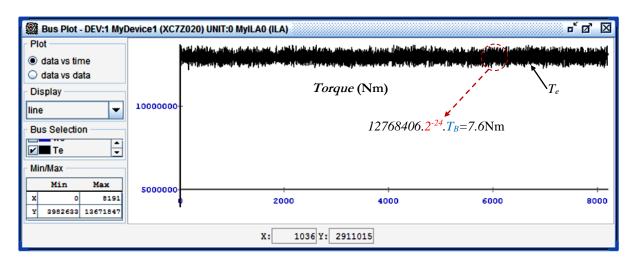

| VHDL simulation results                                                                                                                                                                              |    |

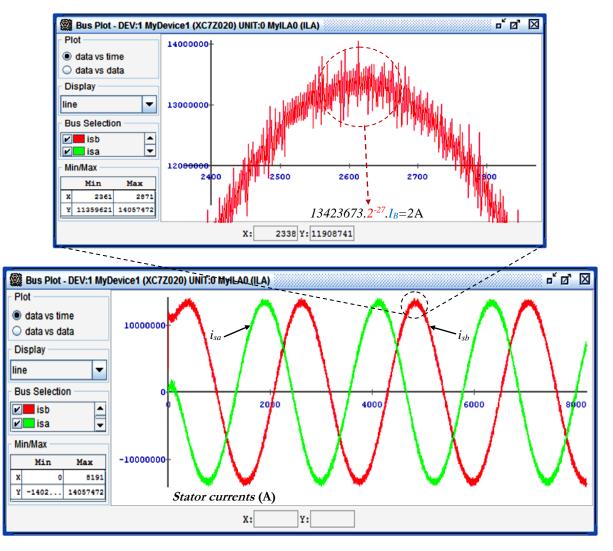

| Figure 3.13:HIL validation of the synchronous machine delta-operator model.                                                                                                                          |    |

| Figure 3.14: Waveform of the electromagnetic torque – HIL testing                                                                                                                                    |    |

| Figure 3.15: Waveforms of the stator currents – HIL testing                                                                                                                                          |    |

| Figure 3.16: Waveforms of rotor position (blue) and rotor speed (red) – HIL testing                                                                                                                  |    |

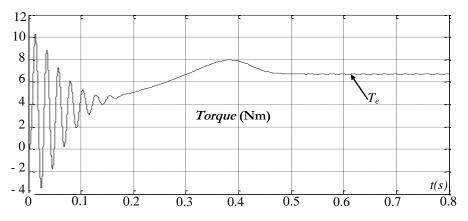

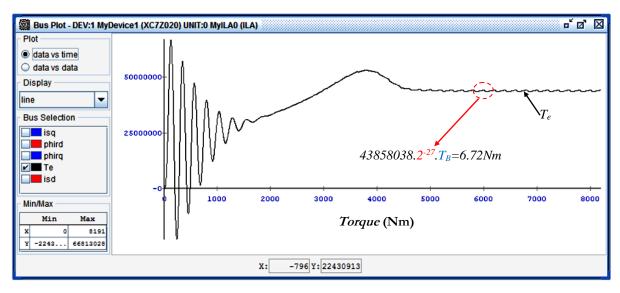

| Figure 3.17: Response of the electromagnetic torque $T_e$                                                                                                                                            |    |

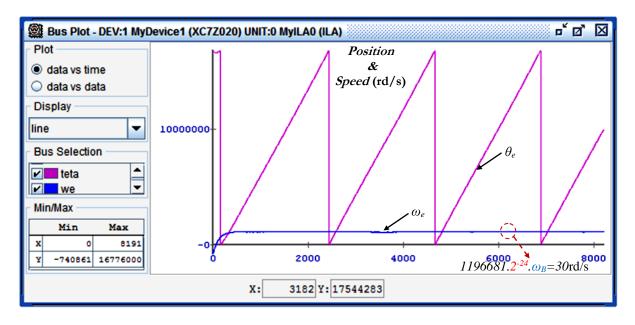

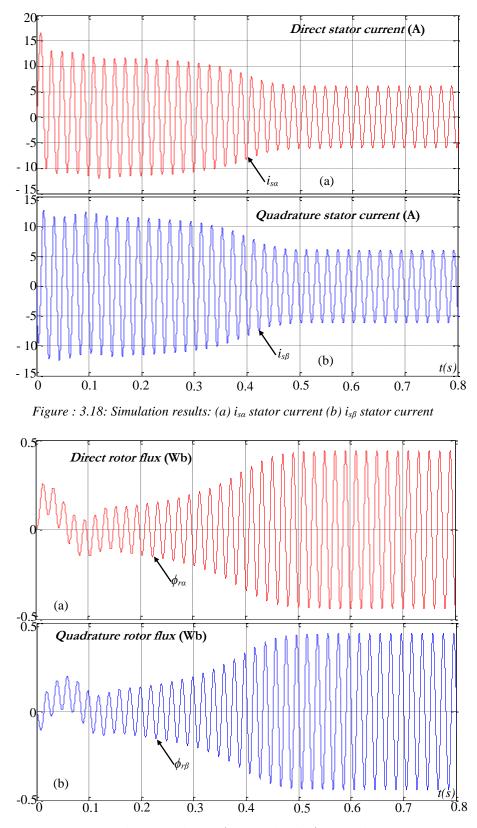

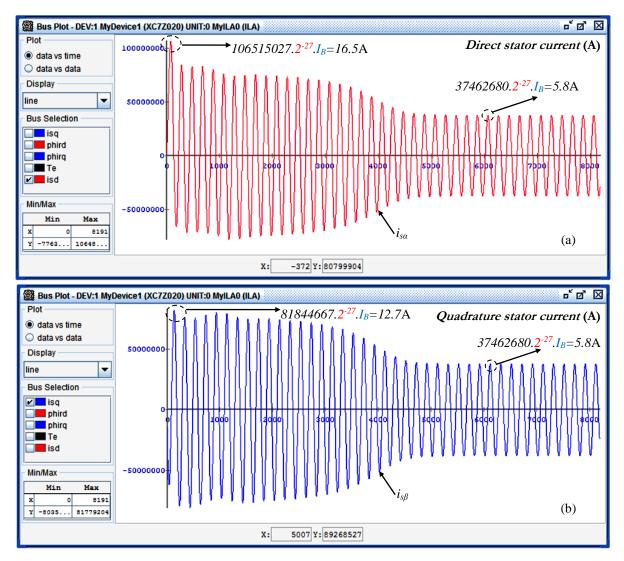

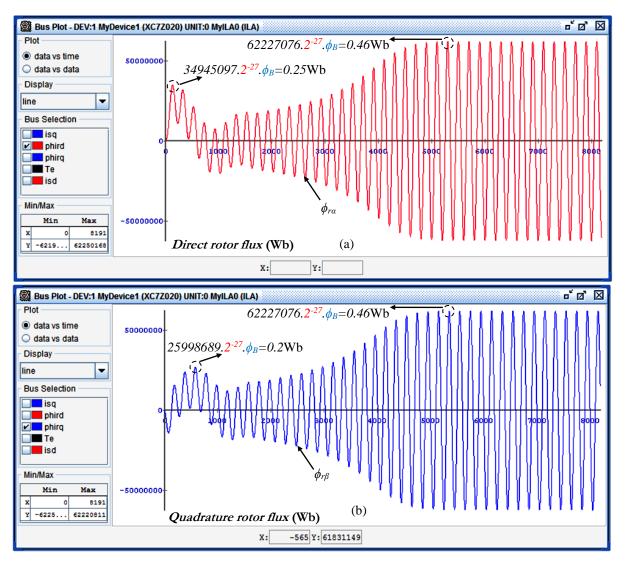

| Figure 5.17: Response of the electromagnetic torque $T_e$<br>Figure : 3.18: Simulation results: (a) $i_{sa}$ stator current (b) $i_{s\beta}$ stator current                                          |    |

| Figure 3.19: Simulation results: (a) $t_{sa}$ statof current (b) $t_{s\beta}$ statof current<br>Figure 3.19: Simulation results: (a) $\phi_{ra}$ rotor flux (b) $\phi_{r\beta}$ rotor flux waveforms |    |

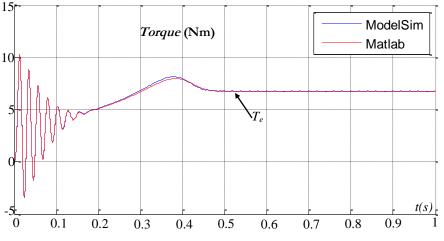

| Figure 3.19: Simulation results. (a) $\varphi_{ra}$ rolof flux (b) $\varphi_{rb}$ rolof flux waveforms<br>Figure 3.20: Matlab and ModelSim simulation results                                        |    |

| Figure 3.20: Manual models in simulation results<br>Figure 3.21: Real-time Waveform of the electromagnetic torque $T_e$                                                                              |    |

| Figure 3.22: Real-time simulations results (a) $i_{s\alpha}$ (b) $i_{s\beta}$                                                                                                                        |    |

| Figure 3.22: Real-time simulations results (a) $t_{sa}$ (b) $t_{s\beta}$<br>Figure 3.23: Real-time simulations results (a) $\phi_{ra}$ (b) $\phi_{r\beta}$                                           |    |

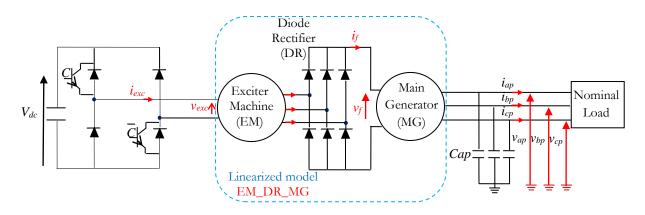

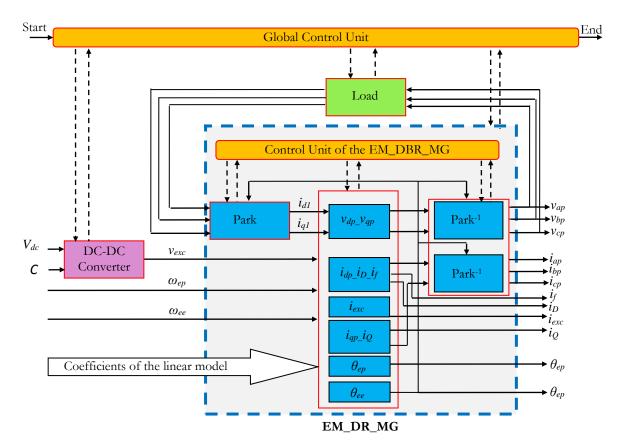

| Figure 3.23: Real-time simulations results (a) $\varphi_{ra}(b) \varphi_{rb}$<br>Figure 3.24: Structure of the three-stage avionics alternator                                                       |    |

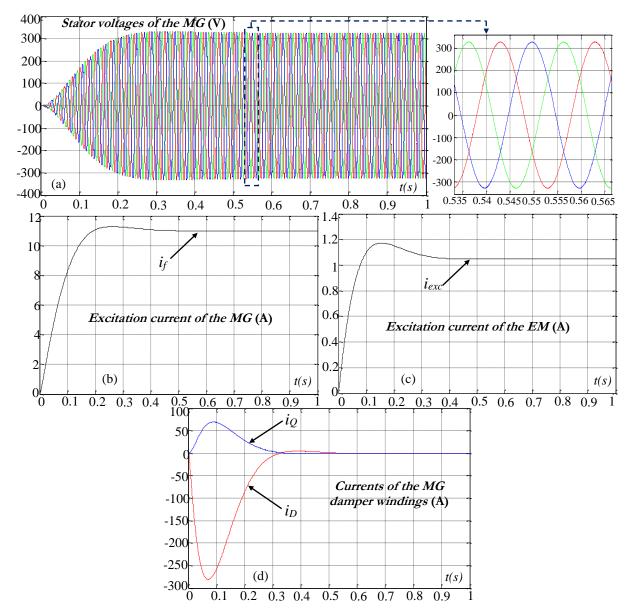

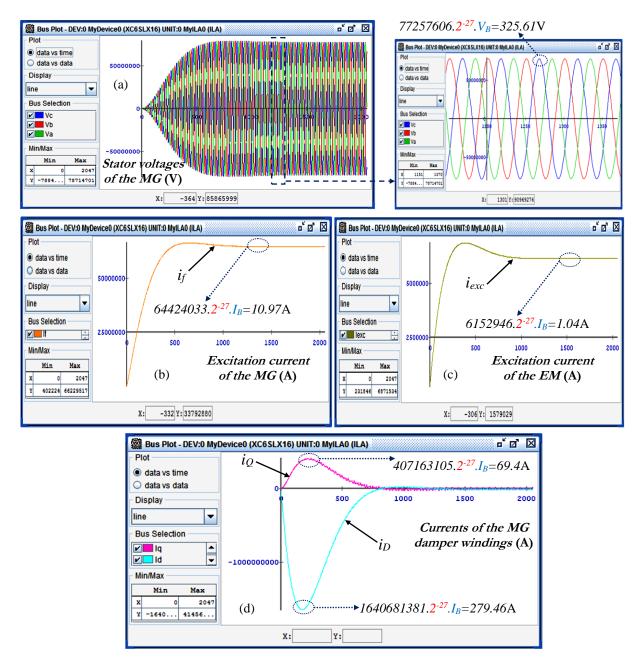

| Figure 3.24: Structure of the infee-stage aviones alternator<br>Figure 3.25: Offline simulation results of the developed digital algorithm a) Simple state                                           |    |

|                                                                                                                                                                                                      |    |

| voltages of the main generator $b$ ) Excitation current of the main generator $c$ ) Excitation                                                                                                       |    |

| current of the exciter machine d) currents of the main generator damper windings<br>Figure 3.26: Global hardware architecture of the embedded three-stage avionics altern                            |    |

| 0 0                                                                                                                                                                                                  |    |

| real-time simulator                                                                                                                                                                                  |    |

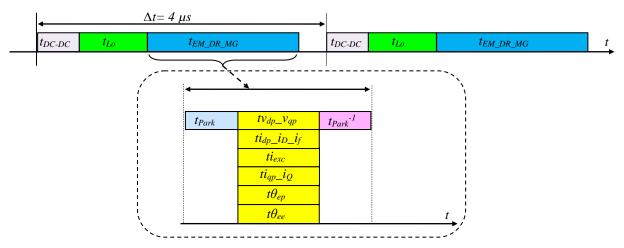

| Figure 3.27: Sequential timing diagram of the developed FPGA-based architecture                                                                                                                      |    |

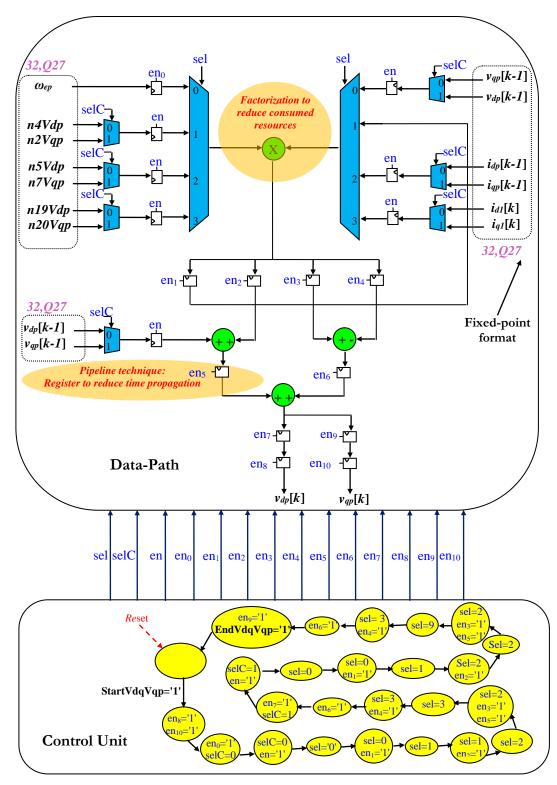

| Figure 3.28: Hardware architecture of the Vdp_Vqp sub-module                                                                                                                                         |    |

| Figure 3.29: Real-time emulation results of the developed FPGA-based architecture (a)                                                                                                                |    |

| Simple stator voltages of the main generator (b) Excitation current of the main generator                                                                                                            |    |

| Excitation current of the exciter machine (d) currents of the main generator damper win                                                                                                              |    |

|                                                                                                                                                                                                      | /0 |

# Chapter 4:

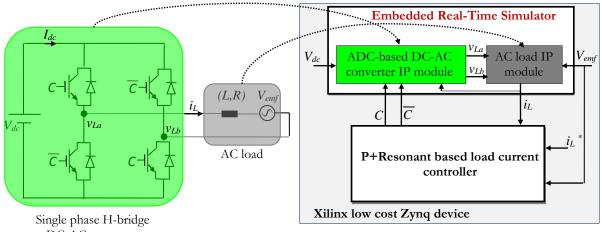

| Figure 4. 1: Structure of the developed control system                         | 73        |

|--------------------------------------------------------------------------------|-----------|

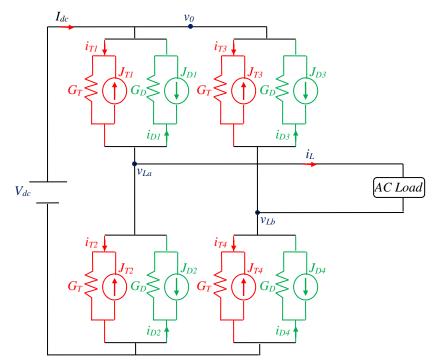

| Figure 4. 2: Equivalent ADC-based model of the single phase DC-AC converter    | 74        |

| Figure 4. 3: ADC-based model of the single phase DC-AC converter – Modular par | titioning |

|                                                                                | 76        |

| Figure 4. 4: AC load current waveform- open loop simulation                    | 77        |

| Figure 4. 5: AC load current waveform – closed loop simulation                 | 78        |

| Figure 4. 6: Designed FPGA architecture of the $i^{th}$ element of the vector $x[k]$    | 79      |

|-----------------------------------------------------------------------------------------|---------|

| Figure 4. 7: AC Load current waveform- open loop offline simulation                     | 79      |

| Figure 4. 8: Timing diagram of the developed simulator                                  | 80      |

| Figure 4. 9: P+Resonant based real-time HIL waveform AC load current                    | 81      |

| Figure 4. 10: Simulated power system (a) topology (b) structure                         | 82      |

| Figure 4. 11: Equivalent ADC-based model of the 3-phase voltage source inverter         |         |

| Figure 4. 12: 3-phase load currents of SimPowerSystems based model and ADC-based        | l model |

|                                                                                         |         |

| Figure 4. 13: Line-to-line voltages of SimPowerSystems based model and ADC-based        | model   |

| model                                                                                   |         |

| Figure 4. 14: Real-time waveform of the load currents                                   | 85      |

| Figure 4. 15: Real-time waveforms of the line-to-line voltages                          |         |

| Figure 4. 16: (a) 3-phase diode rectifier topology (b) equivalent ADC-based model       |         |

| Figure 4. 17 : Diode rectifier DC-link voltage waveform - offline simulation            |         |

| Figure 4. 18: Diode rectifier line currents waveforms - offline simulation              |         |

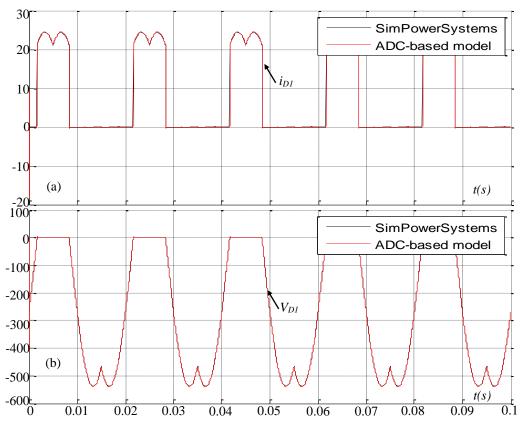

| Figure 4. 19: (a) current of diode 1 (b) voltage of diode 1 - offline simulation        |         |

| Figure 4. 20: Diode rectifier line currents waveforms - real-time simulation            | 90      |

| Figure 4. 21: Diode rectifier DC-link voltage and current and voltage of diode D1 - red |         |

| simulation                                                                              | 91      |

| Chapter 5:                                                                              |         |

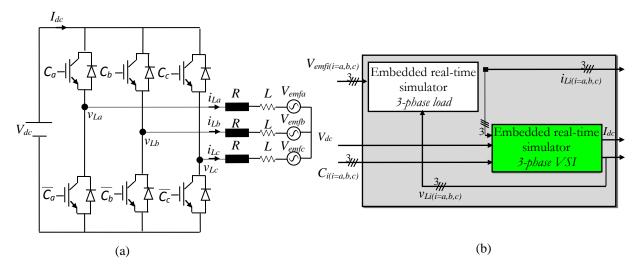

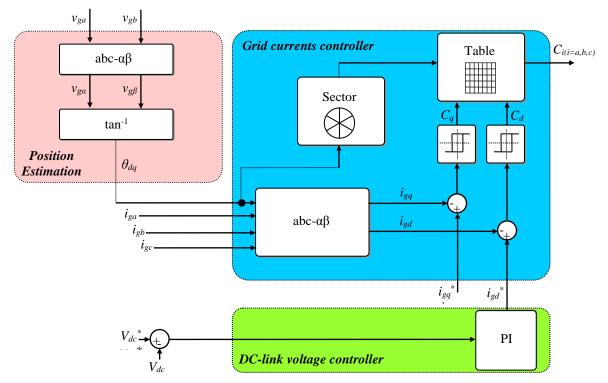

| Figure 5. 1: Structure of the developed control system                                  |         |

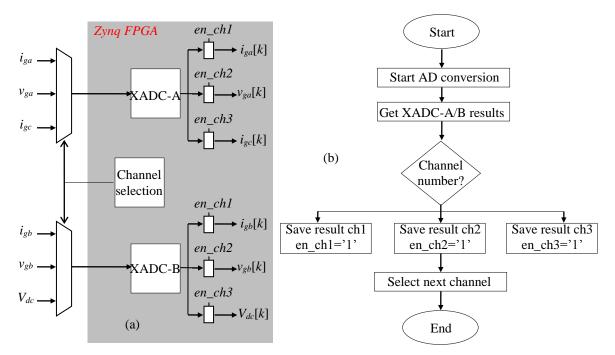

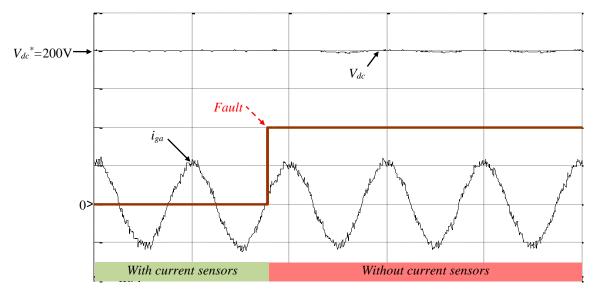

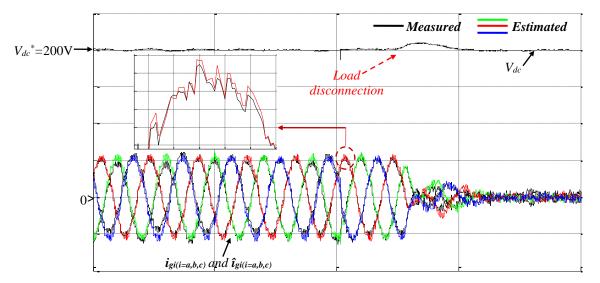

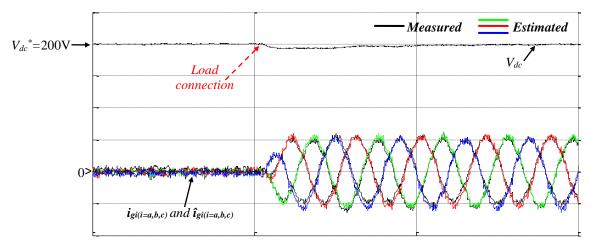

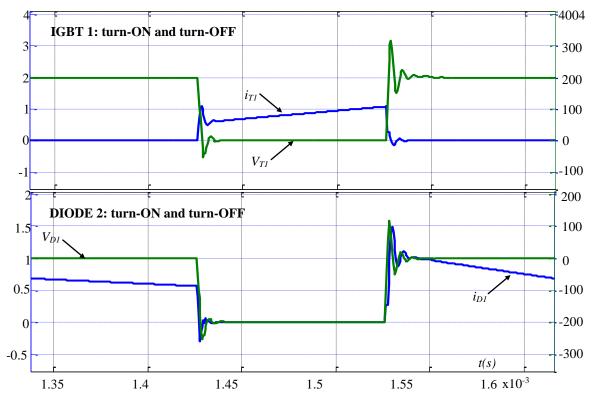

| Figure 5. 2: Synoptic of the DSMP controller94Figure 5. 3: (a) Synoptic of the XADC conversion unit; (b) conversion process95Figure 5. 4: (a) power converter topology; (b) 1-leg equivalent ADC-based circuit; (c)97Ynoptic of the ADC-based model97Figure 5. 5: Offline simulation results during switches commutation98Figure 5. 6: Closed loop offline simulation results during load connection (h: 20ms/div; v:9750V/div, 2.5A/div)99Figure 5. 7: Designed FPGA architecture of the i <sup>th</sup> element of the vector $x[k]$ 100Figure 5. 9: Timing diagram101Figure 5. 10: Closed loop real-time HIL results during (a) load connection and (b) at steady102Figure 5. 11: Experimental setup103Figure 5. 12: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated $v_{La}$ during diode PWMVectifier operation mode when the load is connected (h: 50ms/div; v: 50V/div, 2.5A/div)104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated $v_{La}$ during diode rectifier104Figure 5. 14: Measured V <sub>dc</sub> and i <sub>ga</sub> before and after current sensor fault (h: 20ms/div; v:104                                                                                                                                                                                                                                                                                                                                                      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

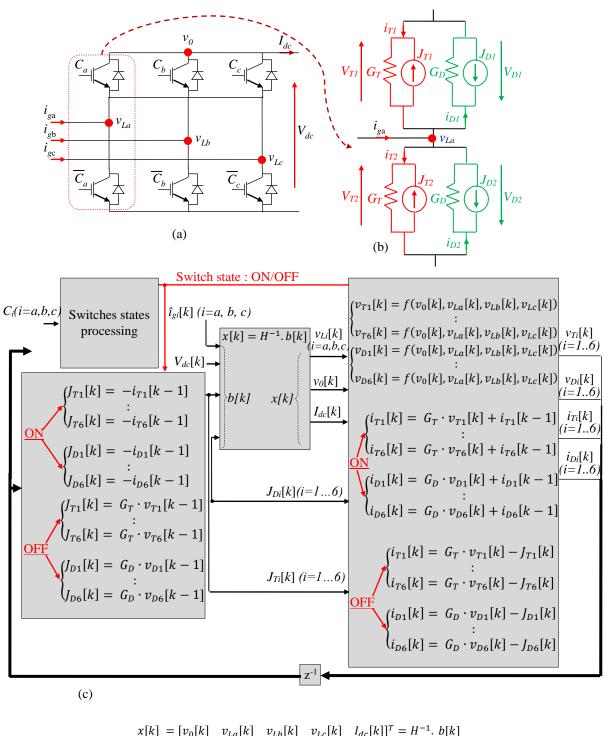

| Figure 5. 4: (a) power converter topology; (b) 1-leg equivalent ADC-based circuit; (c)ynoptic of the ADC-based model97Figure 5. 5: Offline simulation results during switches commutation98Figure 5. 6: Closed loop offline simulation results during load connection (h: 20ms/div; v:50V/div, 2.5A/div)99Figure 5. 7: Designed FPGA architecture of the i <sup>th</sup> element of the vector $x[k]$ 100Figure 5. 8: FPGA-based architecture of the 3-phase RL-filter101Figure 5. 9: Timing diagram101Figure 5. 10: Closed loop real-time HIL results during (a) load connection and (b) at steadytate (h: 50ms/div; v: 50V/div, 2.5A/div)102Figure 5. 11: Experimental setup103Figure 5. 12: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode PWMrectifier operation mode when the load is connected (h: 50ms/div; v: 50V/div, 2.5A/div)104Figure 5. 13: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifieroperation mode when the load is disconnected (h: 50ms/div; v: 50V/div, 2.5A/div)104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ynoptic of the ADC-based model97Figure 5. 5: Offline simulation results during switches commutation98Figure 5. 6: Closed loop offline simulation results during load connection (h: 20ms/div; v:9050V/div, 2.5A/div)99Figure 5. 7: Designed FPGA architecture of the i <sup>th</sup> element of the vector $x[k]$ 100Figure 5. 8: FPGA-based architecture of the 3-phase RL-filter100Figure 5. 9: Timing diagram101Figure 5. 10: Closed loop real-time HIL results during (a) load connection and (b) at steady102Figure 5. 11: Experimental setup103Figure 5. 12: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode PWM104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104 |

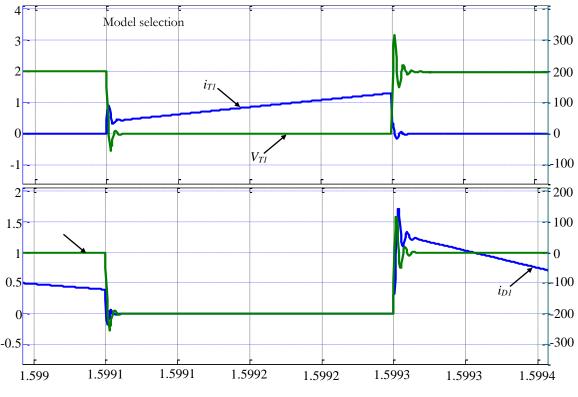

| Figure 5. 5: Offline simulation results during switches commutation98Figure 5. 6: Closed loop offline simulation results during load connection (h: 20ms/div; v:9950V/div, 2.5A/div)99Figure 5. 7: Designed FPGA architecture of the i <sup>th</sup> element of the vector $x[k]$ 100Figure 5. 8: FPGA-based architecture of the 3-phase RL-filter100Figure 5. 9: Timing diagram101Figure 5. 10: Closed loop real-time HIL results during (a) load connection and (b) at steady102Figure 5. 11: Experimental setup103Figure 5. 12: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode PWM104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104                                                                                                                                                                                                                                                                                                                  |

| Figure 5. 6: Closed loop offline simulation results during load connection (h: 20ms/div; v: $50V/div$ , 2.5A/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 50V/div, 2.5A/div)99Figure 5. 7: Designed FPGA architecture of the i <sup>th</sup> element of the vector x[k]100Figure 5. 8: FPGA-based architecture of the 3-phase RL-filter100Figure 5. 9: Timing diagram101Figure 5. 10: Closed loop real-time HIL results during (a) load connection and (b) at steady102tate (h: 50ms/div; v: 50V/div, 2.5A/div)102Figure 5. 11: Experimental setup103Figure 5. 12: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode PWMrectifier operation mode when the load is connected (h: 50ms/div; v: 50V/div, 2.5A/div)104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier104                                                                           |

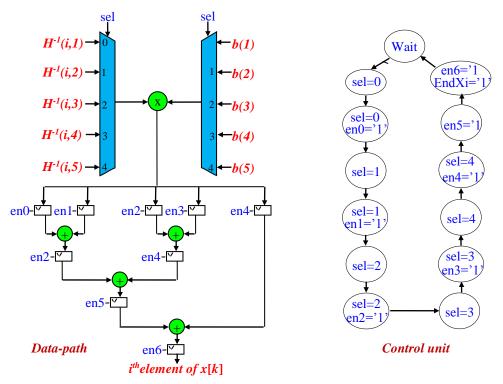

| Figure 5. 7: Designed FPGA architecture of the ith element of the vector $x[k]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

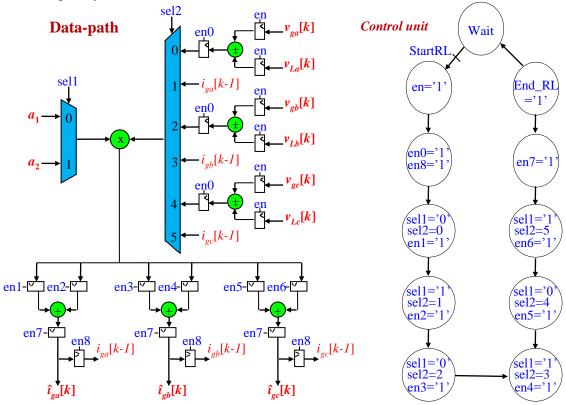

| Figure 5. 8: FPGA-based architecture of the 3-phase RL-filter100Figure 5. 9: Timing diagram101Figure 5. 10: Closed loop real-time HIL results during (a) load connection and (b) at steady102tate (h: 50ms/div; v: 50V/div, 2.5A/div)102Figure 5. 11: Experimental setup103Figure 5. 12: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode PWMrectifier operation mode when the load is connected (h: 50ms/div; v: 50V/div, 2.5A/div)104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifieroperation mode when the load is connected (h: 50ms/div; v: 50V/div, 2.5A/div)104Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifieroperation mode when the load is disconnected (h: 50ms/div; v: 50V/div, 2.5A/div)104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

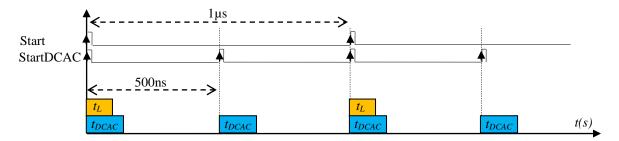

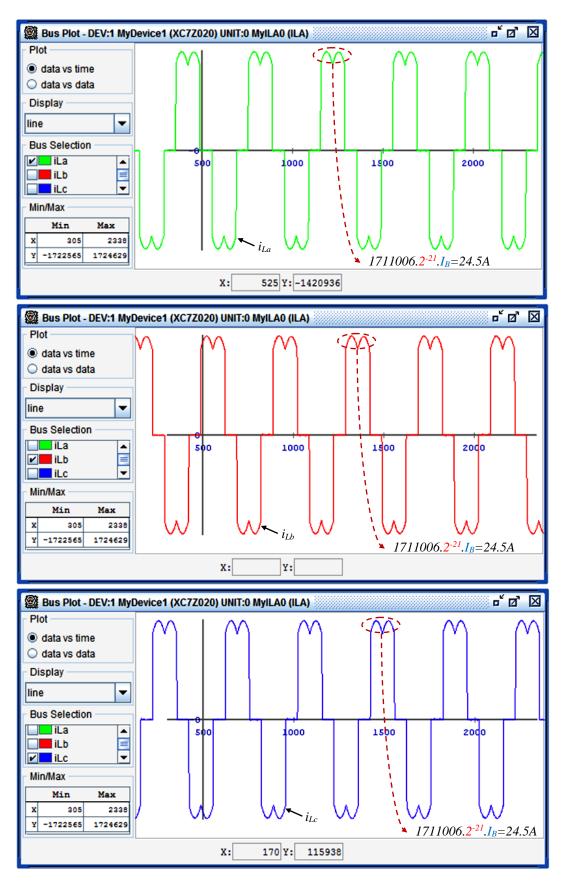

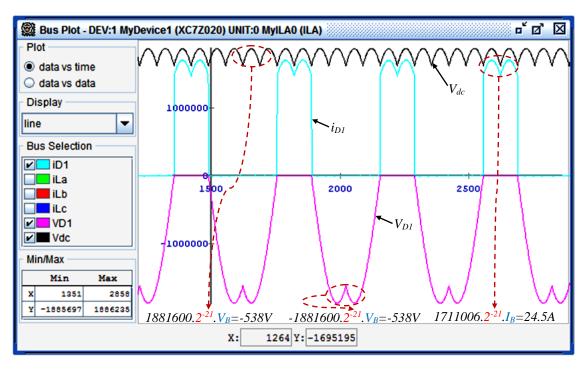

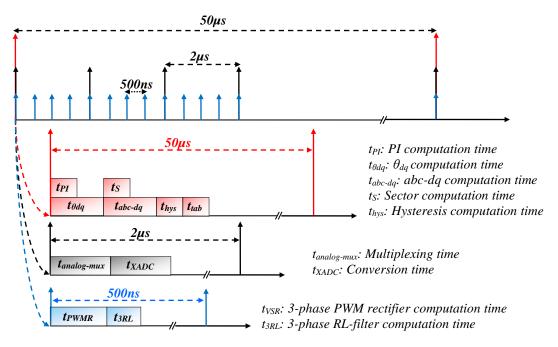

| Figure 5. 9: Timing diagram101Figure 5. 10: Closed loop real-time HIL results during (a) load connection and (b) at steady102tate (h: $50ms/div$ ; v: $50V/div$ , $2.5A/div$ )102Figure 5. 11: Experimental setup103Figure 5. 12: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode PWMrectifier operation mode when the load is connected (h: $50ms/div$ ; v: $50V/div$ , $2.5A/div$ )104Figure 5. 13: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V_{dc}, measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V_{dc}, measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V_{dc}, measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

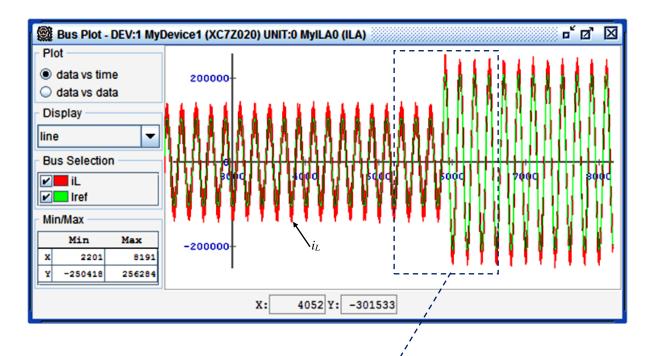

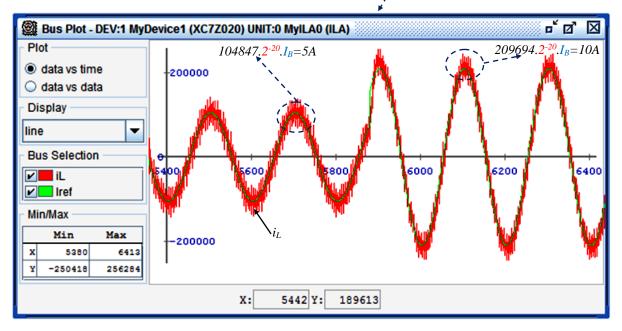

| Figure 5. 9: Timing diagram101Figure 5. 10: Closed loop real-time HIL results during (a) load connection and (b) at steady102tate (h: $50ms/div$ ; v: $50V/div$ , $2.5A/div$ )102Figure 5. 11: Experimental setup103Figure 5. 12: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode PWMrectifier operation mode when the load is connected (h: $50ms/div$ ; v: $50V/div$ , $2.5A/div$ )104Figure 5. 13: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V_{dc}, measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V_{dc}, measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104Figure 5. 13: Measured V_{dc}, measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| tate (h: 50ms/div; v: 50V/div, 2.5A/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Figure 5. 11: Experimental setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

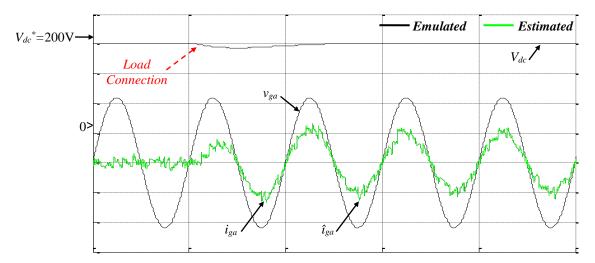

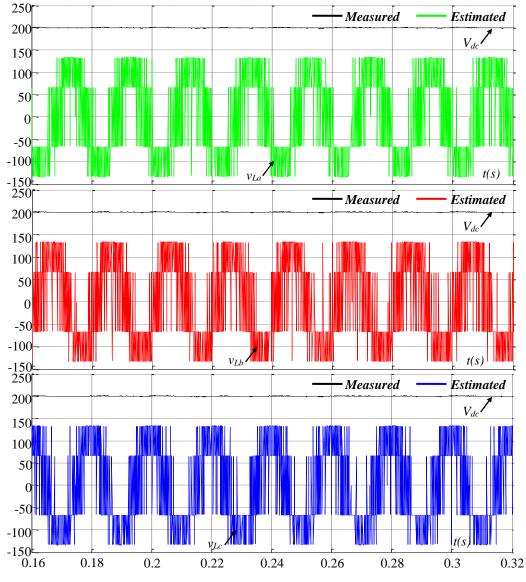

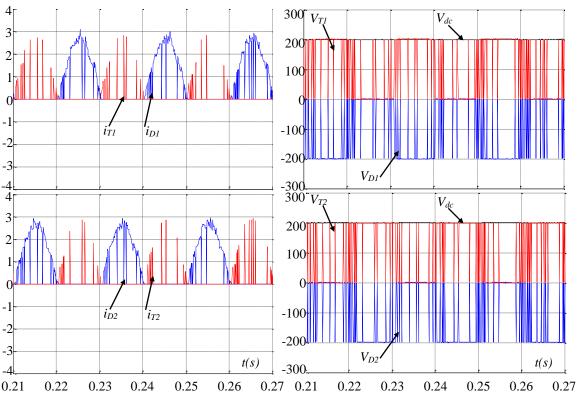

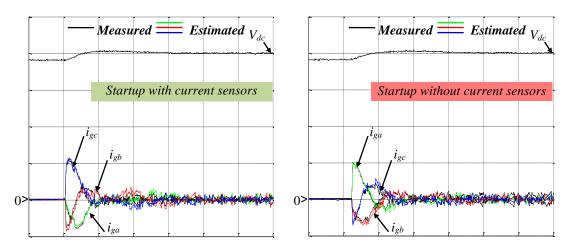

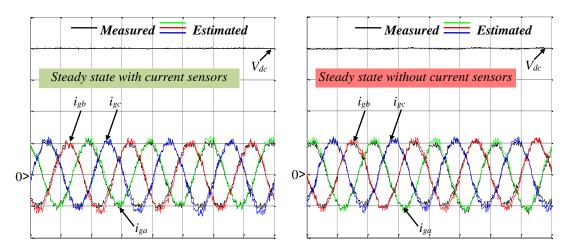

| Figure 5. 12: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode PWM vectifier operation mode when the load is connected (h: 50ms/div; v: 50V/div, 2.5A/div) 104 Figure 5. 13: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier operation mode when the load is connected (h: 50ms/div; v: 50V/div, 2.5A/div) 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| rectifier operation mode when the load is connected (h: 50ms/div; v: 50V/div, 2.5A/div) 104<br>Figure 5. 13: Measured V <sub>dc</sub> , measured and estimated i <sub>ga</sub> , estimated v <sub>La</sub> during diode rectifier<br>operation mode when the load is disconnected (h: 50ms/div; v: 50V/div, 2.5A/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 5. 13: Measured $V_{dc}$ , measured and estimated $i_{ga}$ , estimated $v_{La}$ during diode rectifier pperation mode when the load is disconnected (h: 50ms/div; v: 50V/div, 2.5A/div)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| operation mode when the load is disconnected (h: 50ms/div; v: 50V/div, 2.5A/div)104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

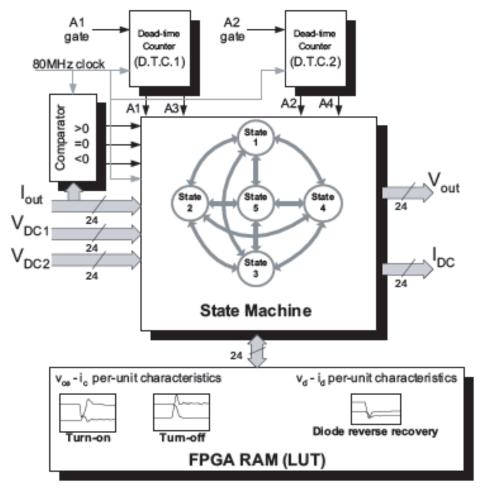

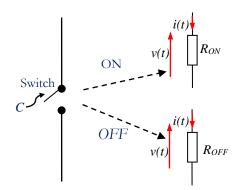

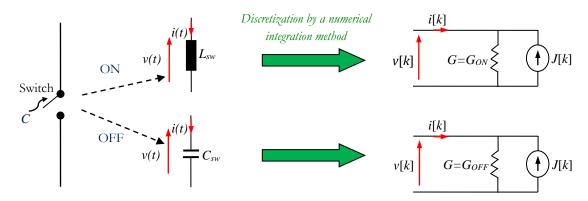

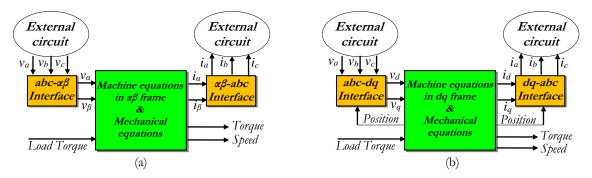

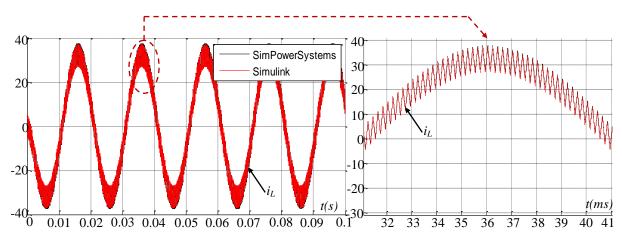

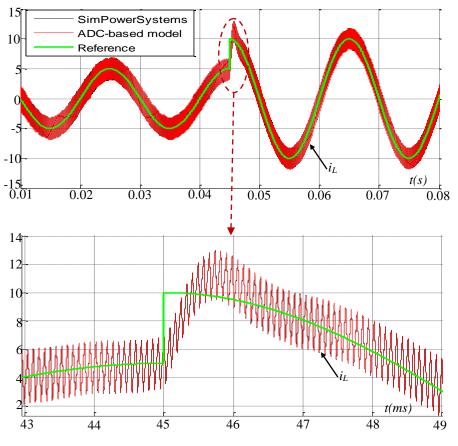

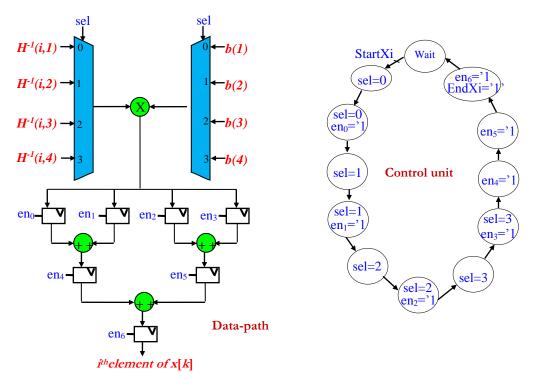

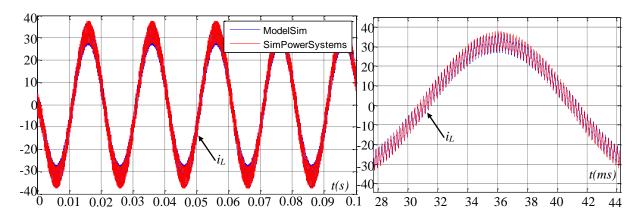

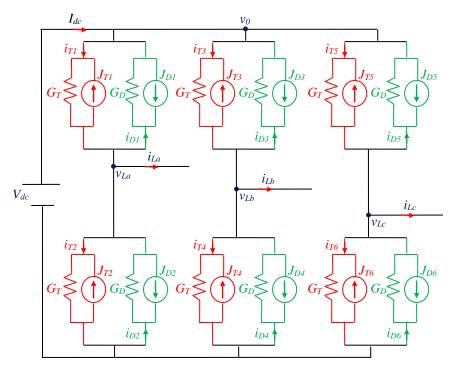

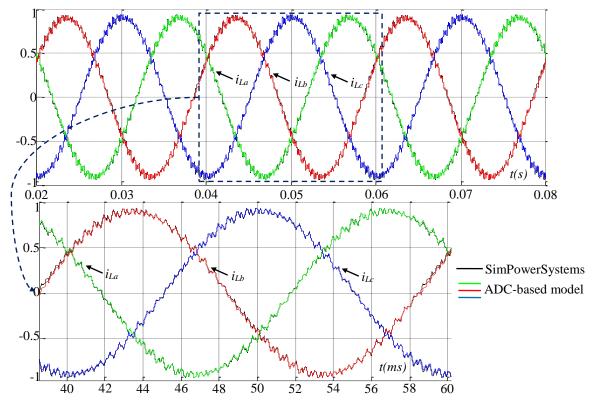

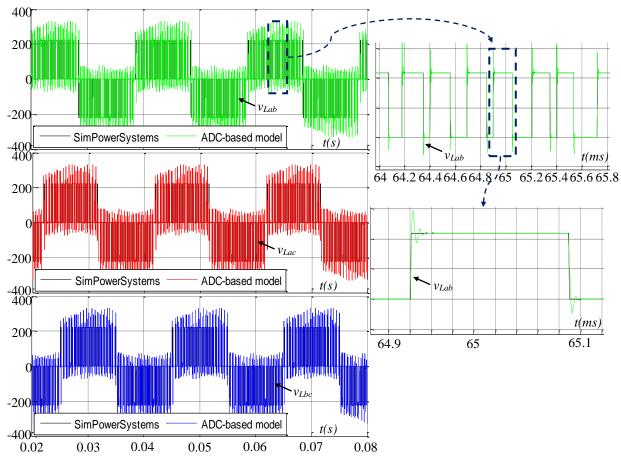

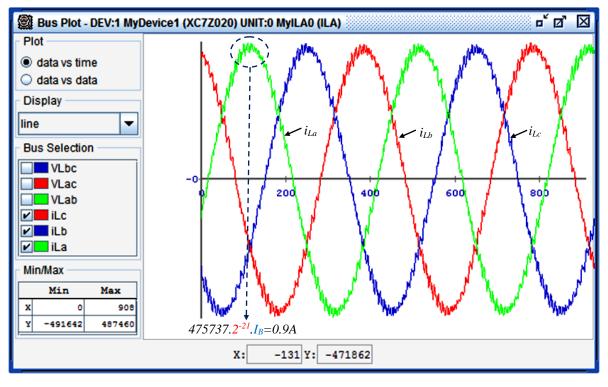

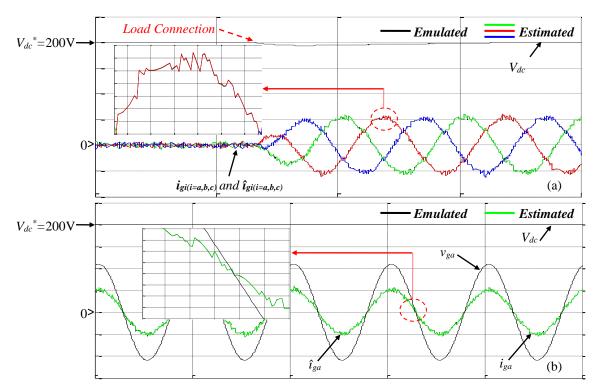

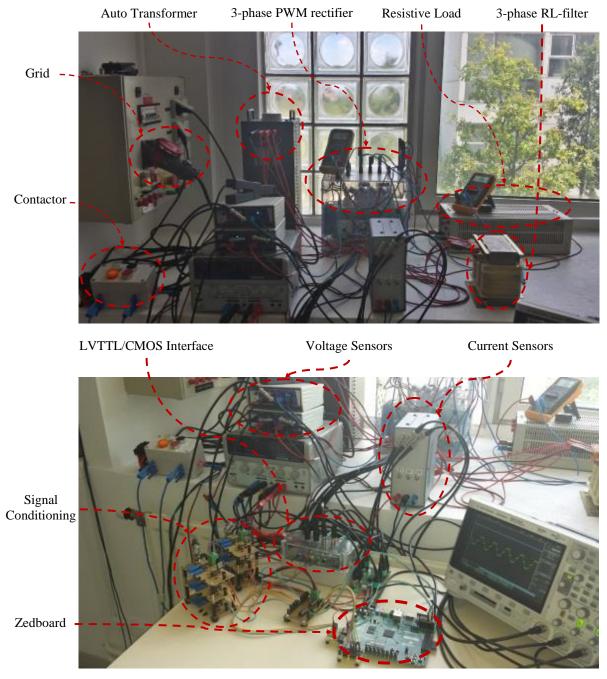

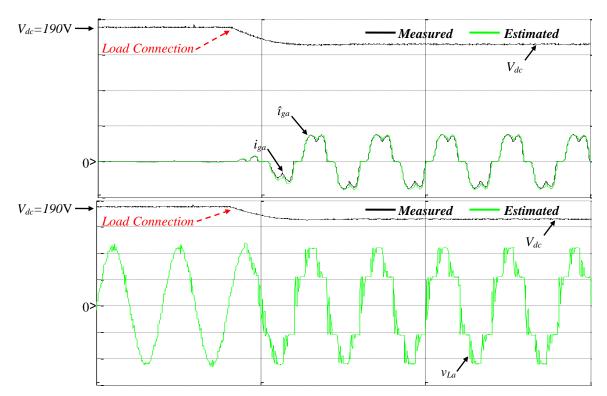

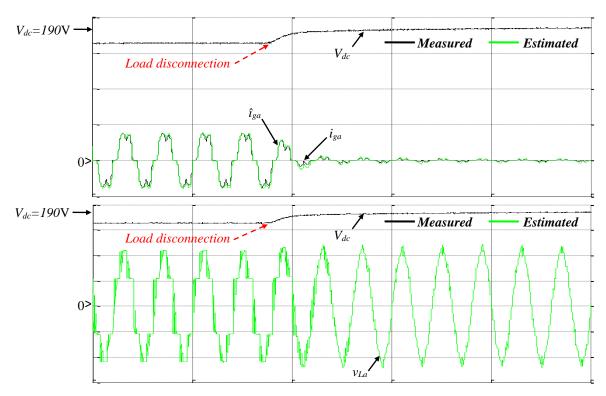

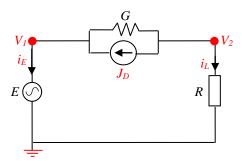

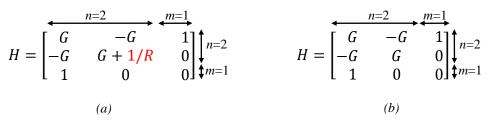

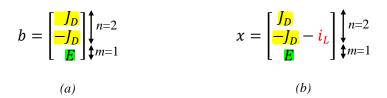

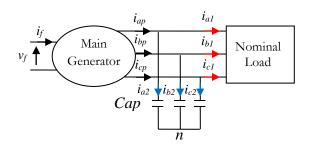

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |