## THÈSE

présentée

à l'Université de Cergy-Pontoise École Nationale Supérieure de l'Électronique et de ses Applications

pour obtenir le grade de :

Docteur en Science de l'Université de Cergy-Pontoise Spécialité : Sciences et Technologies de l'Information et de la Communication

Par

## **Bilal Shams**

Équipes d'accueil : Équipe Traitement des Images et du Signal (ETIS) - CNRS UMR 8051 et Digital Solutions for Innovative IPs Team - STMicroelectronics Crolles

Titre de la thèse :

## Les codes LDPC non-binaire du nouvelle generation

Soutenue le 08-12-2010 devant la commission d'examen composée de :

| Didier Demigny       | IUT (Lannion), Université Rennes-1  | Examinateur        |

|----------------------|-------------------------------------|--------------------|

| Valentin Savin       | CETA-LETI, Grenoble                 | Examinateur        |

| Emmanuel Boutillon   | LAB-STICC, UBO, Lorient             | Rapporteur         |

| Laura Conde-Canencia | LAB-STICC, UBO, Lorient             | Rapporteur         |

| Dr. Jossy Sayir      | University of Cambridge, UK         | Rapporteur         |

| Vincent HEINRICH     | STMicroelectronics, Crolles         | Encadrant          |

| David DECLERCQ       | ENSEA - Université de Cegy Pontoise | Directeur de thèse |

# **Author's Publications**

#### ■ INTERNATIONAL CONFERENCES

$[C_1]$  <u>B. Shams</u>, D. Declercq, V. Y. Heinrich, "Non-binary split LDPC codes defined over finite groups", in Proc. of IEEE ISWCS'09, Siena-Tuscany, Italy, Sept. 2009

$[C_2]$  <u>B. Shams</u>, D. Declercq, V. Y. Heinrich, "Improved decoding architecture for nonbinary split codes defined over finite groups", in Proc. of IEEE ICFCC'10, Wuhan, China, May 2010

# **Dedication**

To Dr. Shams Rahman, my dad also a Ph.D. who is in the Heavens now

## Acknowledgements

I carried out my thesis at the laboratory ETIS (Equipe Traitment d'Image et du Signal) at ENSEA (Ecole Nationale Supérieure de l'Electronique et ses Application and STMicroelectronics, crolles.

I would like to thank both teams at ETIS and STMicroelectronics, who welcomed me into their teams and gave me the oppertunity to develop myself into a better professional.

My foremost thanks to Prof. David Declercq who supervised me during my Ph.D. He has always been kind, patient and encouraging. I take great pride in having to work with him, who is a big name in the field of LDPC codes. I feel greatly indebted to him and I have learnt a lot from him.

My utmost gratitudes for Vincent Heinrich who was my supervisor at STMicroelectronics. He has always been cool, calm and dynamic. He has taught me a lot about the corporate sector.

I would also like to mention the support of my darling wife Zakia durig my Ph.D. She has always been encouraging and motivated me during my hard times.

Above all, I am thankful to the Almighty for His guidance and the blessings he has always been showering on us all.

## Abstract

In this thesis we present our work in the domain of non-binary decoding algorithm for general classes of non-binary LDPC codes. Binary Low-Density Parity-Check (LDPC) codes were originally presented by Gallager in 1963, and after some fundamental theoretical advancement, they were considered in standards like DVB-S2, WI-MAX, DSL, W-LAN etc. Later on, Non-Binary LDPC (NB-LDPC) codes were proposed in literature, and showed better performance for small lengths or when used on non-binary channels. However, the advantages of using NB-LDPC codes come with the consequence of a heavily increased decoding complexity. For a code defined in GF(q), the complexity is of the order  $\mathcal{O}(q^2)$ . Similarly, the memory required for storing messages is of order  $\mathcal{O}(q)$ . Consequently, the implementation of an LDPC-decoder defined over a field order q > 64 becomes practically impossible. The main objective of the thesis is to develop reduced complexity algorithms for non-binary LDPC codes that exhibit excellent performance and are practically implementable. For better decoding performance, not only the decoding algorithm is important, but also the structure of the code plays an important role. With this goal in mind, a new family of codes called cluster-NB-LDPC codes was developed and specific improvements of the NB decoder for cluster-NB-LDPC codes were proposed. Our principal result is that we were able to propose decoders for cluster-NB-LDPC codes with reduced complexity compared to usual decoders for NB-LDPC codes on fields, without any performance loss in error correction capability.

#### Acknowledgements

In the first part of the thesis, we modify the EMS algorithm for cluster codes. We see that the direct implementation of the EMS algorithm to NB cluster-LDPC codes is not a feasible option. There is a loss in performance and an increase in decoding complexity. Therefore, we propose some modification in the procedure, which not only significantly improves the decoding performance but also decreases the decoding complexity. It places the same limits on the number of operations at the check nodes as the EMS algorithm for GF(q)-codes i.e.  $O(n_m log n_m)$ , with  $n_m << q$ . We then propose another method, based on the diversity of cluster codes, to improve the performance of the EMS algorithm for cluster codes. It also helps in reducing the overall complexity of the decoder. In the end we compare the decoding performance using this method and analyze the effect on the decoding complexity.

In the last part of the chapter, we propose a new direction for the decoding of LDPC codes. It is based on the creation of lists of codewords that are local to the parity check nodes. The list is constructed recursively in a tree structure, which makes it a good candidate for hardware implementation. It is a new method and requires further improvement. As an initial report, we have obtained good results with less number of computations.

Keywords: Non-binary LDPC codes, simplified decoding of non-binary LDPC codes, EMS decoding algorithm, Non-binary cluster LDPC codes, local list based decoding

## Résumé

Dans cette thèse, nous présentons nos travaux dans le domaine des algorithmes de décodage des codes LDPC non-binaires généralisés. Les codes LDPC binaires ont été initialement proposés par Gallager en 1963, et après quelques avancées théoriques fondamentales, ils ont été proposés dans des standards tels que DVB-S2, WI-MAX, DSL, W-LAN etc. Plus tard, les codes LDPC non-binaires (NB-LDPC) ont été proposés dans la littérature, et ont montré une meilleure performance pour de petites tailles de code ou lorsqu'ils sont utilisés sur des canaux non-binaires. Cependant, les avantages de l'utilisation de codes NB-LDPC impliquent une augmentation importante de la complexité de décodage. Pour un code défini dans un corps de Galois GF(q), la complexité est d'ordre  $\mathcal{O}(q^2)$ . De même, la mémoire requise pour le stockage des messages est d'ordre  $\mathcal{O}(q)$ . Ainsi, l'implémentation d'un décodeur LDPC défini sur un corps de Galois pour q > 64 devient impossible dans la pratique. L'objectif principal de cette thèse est de développer des algorithmes avec une bonne performance et complexité réduite de sorte qu'ils deviennent implémentables. Pour une performance de décodage optimisée, non seulement l'algorithme est important, mais également la structure du code joue un rôle clé. Avec cet objectif à l'esprit, une nouvelle famille de codes appelés « cluster-NB-LDPC codes » a été élaborée ainsi que des améliorations spécifiques du décodeur non-binaire pour ces codes. Le résultat principal est que nous avons pu proposer des décodeurs pour les codes cluster-NB-LDPC avec une complexité réduite par rapport aux décodeurs classiques pour les codes NB-LDPC définis sur les corps de Galois, sans aucune perte de performance dans la capacité de correction

#### Résumé

#### d'erreur.

Dans la première partie de la thèse, nous avons modifié l'algorithme EMS pour les cluster-codes. La généralisation directe de l'algorithme EMS aux codes cluster-NB-LDPC n'est pas réaliste . Il y a une perte de performance et une augmentation de la complexité. Par conséquent, nous proposons quelques modifications dans la procédure, qui non seulement améliore considérablement les performances de décodage, mais diminue également la complexité. Au niveau des noeuds de parité, cet algorithme conserve les mêmes limites sur le nombre d'opérations que l'algorithme EMS pour GF(q)-codes,  $\mathcal{O}(n_m log n_m)$  avec  $n_m << q$ . Nous proposons ensuite une autre méthode, basée sur la diversité des codes cluster, afin d'améliorer les performances de l'algorithme EMS pour les codes cluster-LDPC. Il contribue également à réduire la complexité globale du décodeur. Finalement, nous comparons les performances de décodage.

Dans la dernière partie du chapitre, nous proposons une nouvelle direction pour le décodage des codes LDPC. Elle est basée sur la création des listes des mots de code qui correspondent à des noeuds de parité. Les listes sont construite de manière récursive dans une structure en arbre, ce qui en fait un bon candidat pour l'implémentation matérielle. Il s'agit d'une méthode nouvelle et doit encore être améliorée mais à premiére vue nous avons obtenu de bons résultats avec un nombre réduit d'operations.

Mots de clé: Les codes LDPC non-binaires, décodage simplifié des codes LDPC nonbinaires, L'algorithme EMS, cluster-LDPC codes non-binaires, décodage basée sur les listes

# Contents

| Li | st of l | Figures       |                                                | xi  |

|----|---------|---------------|------------------------------------------------|-----|

| Li | st of [ | <b>Fables</b> |                                                | xiv |

| A  | bbrev   | iations       |                                                | XV  |

| 1  | Intr    | oductio       | on - Context and Background                    | 1   |

|    | 1.1     | Contex        | xt and background                              | 1   |

|    |         | 1.1.1         | Introduction                                   | 1   |

|    |         | 1.1.2         | History                                        | 3   |

|    | 1.2     | Motiva        | ation and objective of the thesis              | 4   |

|    | 1.3     | Thesis        | organization                                   | 5   |

| 2  | Non     | -binary       | LDPC codes                                     | 8   |

|    | 2.1     | Classi        | fication of Non-binary LDPC codes              | 8   |

|    |         | 2.1.1         | NB-LDPC codes defined on finite Galois fields  | 9   |

|    |         | 2.1.2         | NB-LDPC codes defined on general linear groups | 24  |

|    |         | 2.1.3         | Cluster NB-LDPC codes defined on Groups        | 29  |

|    | 2.2     | Simpli        | ified implementation of NB-LDPC decoders       | 33  |

|    |         | 2.2.1         | FFT-based BP algorithm                         | 34  |

|    |         | 2.2.2         | Log-FFT belief propagation algorithm           | 37  |

|    |         | 2.2.3         | The log domain non-binary BP algorithm         | 39  |

|   |      | 2.2.4   | The Extended Min-Sum algorithm                     | 41 |

|---|------|---------|----------------------------------------------------|----|

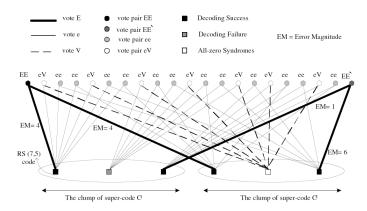

|   |      | 2.2.5   | Symbol Flipping based decoding                     | 46 |

|   |      | 2.2.6   | Non-binary Stochastic decoders                     | 48 |

|   | 2.3  | Compl   | lexity comparison of NB-LDPC decoders              | 51 |

|   | 2.4  | Conclu  | usion                                              | 53 |

| 3 | Imp  | roved E | EMS algorithm for cluster codes                    | 56 |

|   | 3.1  | Genera  | alization of EMS to cluster codes                  | 56 |

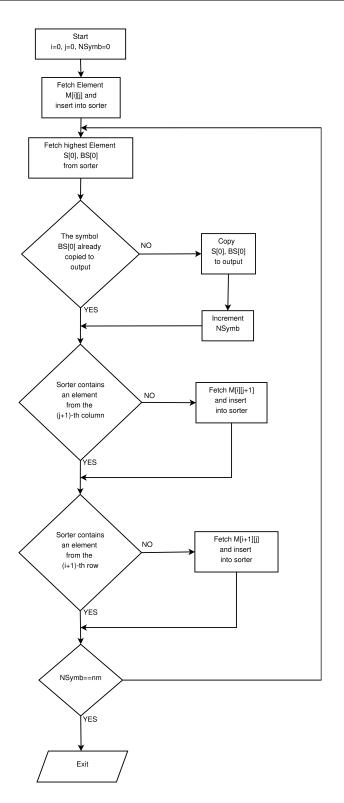

|   |      | 3.1.1   | The decoding algorithm                             | 58 |

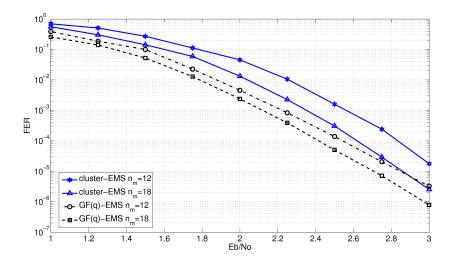

|   |      | 3.1.2   | Monte-Carlo simulation results                     | 61 |

|   | 3.2  | Improv  | ved EMS decoder for cluster codes                  | 65 |

|   |      | 3.2.1   | A second elementary process                        | 65 |

|   |      | 3.2.2   | Improved estimation of output LLRs                 | 67 |

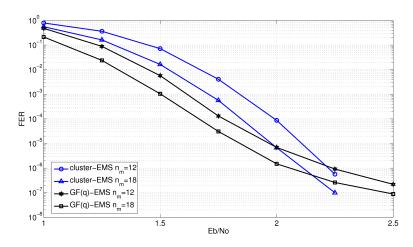

|   |      | 3.2.3   | Monte-Carlo simulation results                     | 68 |

|   |      | 3.2.4   | Hardware Architecture                              | 70 |

|   |      | 3.2.5   | Complexity comparison                              | 73 |

|   | 3.3  | Divers  | ity of group-LDPC codes                            | 75 |

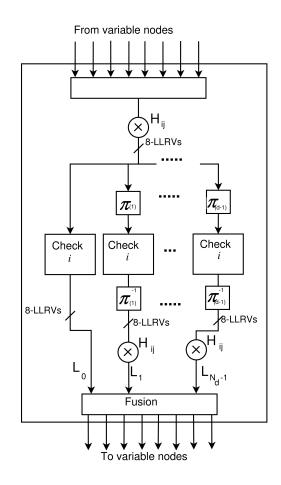

|   |      | 3.3.1   | Parallel cluster-EMS check update processes        | 75 |

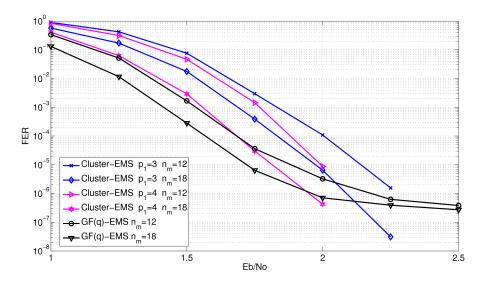

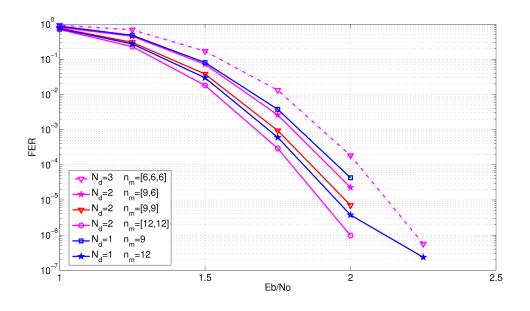

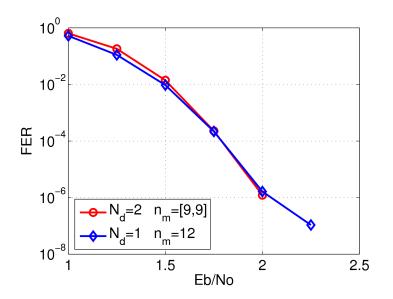

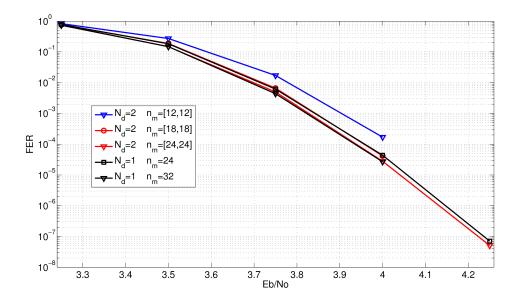

|   |      | 3.3.2   | Monte-Carlo simulation results                     | 77 |

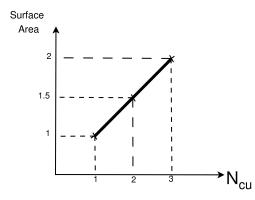

|   |      | 3.3.3   | Complexity comparisons                             | 79 |

|   | 3.4  | Conclu  | usion                                              | 81 |

| 4 | A ne | ew deco | ding algorithm for NB-LDPC codes using local lists | 83 |

|   | 4.1  | List D  | ecoding                                            | 84 |

|   | 4.2  | The lo  | cal-list based decoder                             | 85 |

|   |      | 4.2.1   | Creation of the list                               | 86 |

|   |      | 4.2.2   | Extraction of LLRs from a local list               | 88 |

|   |      | 4.2.3   | The decoding algorithm                             | 89 |

## Contents

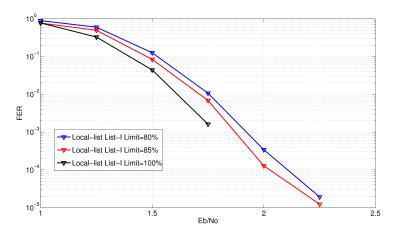

|    | 4.3    | Decoding performance and complexity | 91 |

|----|--------|-------------------------------------|----|

|    | 4.4    | Reduced list-size decoder           | 93 |

|    | 4.5    | Conclusion                          | 95 |

| 5  | Con    | clusions and perspectives           | 96 |

|    | 5.1    | Conclusions                         | 96 |

|    | 5.2    | Perspectives                        | 97 |

| Bi | bliogi | aphy                                | 99 |

# List of Figures

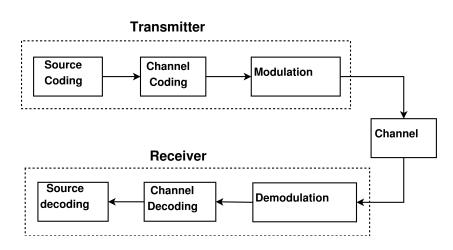

| 1.1  | Block Diagram of a communication system                                                   | 2  |

|------|-------------------------------------------------------------------------------------------|----|

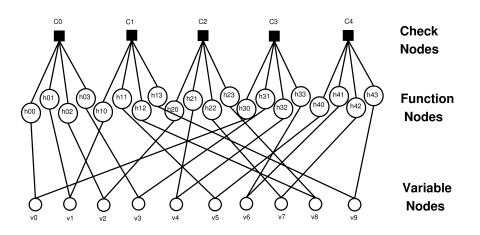

| 2.1  | A non-binary LDPC parity check matrix                                                     | 11 |

| 2.2  | The Tanner Graph for a non-binary parity check matrix                                     | 12 |

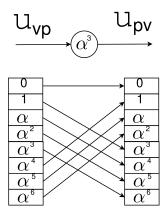

| 2.3  | A cyclic permutation of a message at the permutation node                                 | 13 |

| 2.4  | Binary representation of a GF(q)-LDPC code                                                | 14 |

| 2.5  | The messages flowing across a Tanner graph for the BP algorithm                           | 16 |

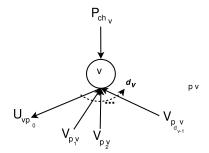

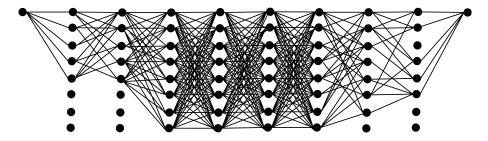

| 2.6  | The degree $d_v$ variable node update                                                     | 17 |

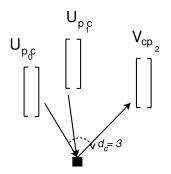

| 2.7  | The degree $d_c = 3$ check node update $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 18 |

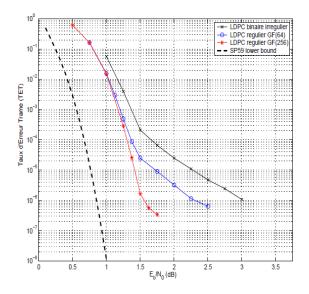

| 2.8  | Binary vs non-binary LDPC codes, $N_b = 3008$ bits and $R = 1/2$                          | 21 |

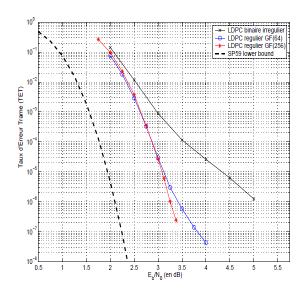

| 2.9  | Binary vs non-binary LDPC codes, $N_b = 565$ bits and $R = 2/3$                           | 21 |

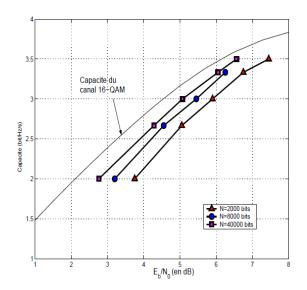

| 2.10 | Performance of regular $GF(256){\rm LDPC}$ codes over a 16-QAM channel                    |    |

|      | at a BER of $10^{-5}$                                                                     | 22 |

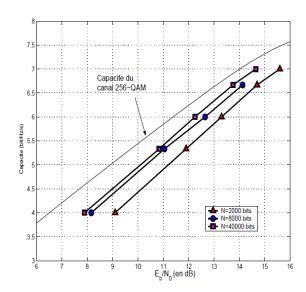

| 2.11 | Performance of regular $GF(256)$ LDPC codes over a 256-QAM chan-                          |    |

|      | nel at a BER of $10^{-5}$                                                                 | 23 |

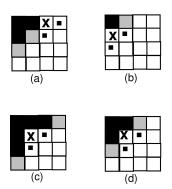

| 2.12 | The square clusters in a binary PCM                                                       | 25 |

| 2.13 | Binary clusters and their associated functions (a). Full-Rank (b) Rank-                   |    |

|      | deficient                                                                                 | 26 |

| 2.14 | A rectangular cluster and its associated function node projections                        | 30 |

| 2.15 | A binary parity check matrix with rectangular clusters                                    | 31 |

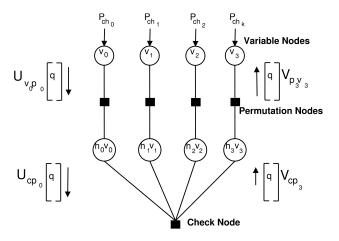

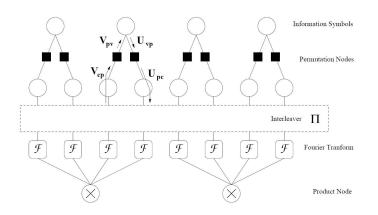

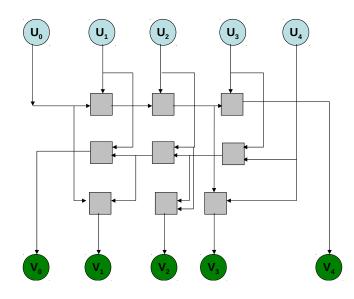

| 2.16 | Tanner graph for FFT-based BP decoding                                                    | 37 |

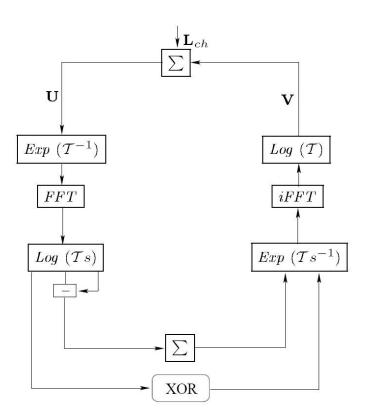

| 2.17 | The log-FFT based BP algorithm                                                | 40 |

|------|-------------------------------------------------------------------------------|----|

| 2.18 | The forward-backward strategy for a check node of degree $d_c=5$ $\ .$ .      | 43 |

| 2.19 | The elementary check update process                                           | 46 |

| 2.20 | Parity check matrix $H$ of a generalized LDPC code based on super-codes       | 46 |

| 2.21 | Tanner Graph and vote generation for the PCM for super-codes based            |    |

|      | generalized LDPC codes                                                        | 47 |

| 2.22 | The Stochastic variable update process for a degree $d_v = 2$                 | 50 |

| 2.23 | The stochastic check update process for degree $d_c = 4$                      | 51 |

| 3.1  | A binary PCM composed of clusters of different sizes                          | 57 |

| 3.2  | The messages flowing across a Tanner graph for cluster-LDPC codes .           | 57 |

| 3.3  | Elementary check update process, various scenarios for adding neigh-          |    |

|      | bors to the sorter                                                            | 61 |

| 3.4  | Flow chart for the check update algorithm                                     | 62 |

| 3.5  | EMS for a $GF(64)$ -code and cluster-code with $p_1 = 4$ , $p_2 = 6$ , $N =$  |    |

|      | 576-bits and $R = 1/2$                                                        | 63 |

| 3.6  | EMS for a $GF(64)$ -code and cluster-code with $p_1 = 4$ , $p_2 = 6$ , $N =$  |    |

|      | 2304-bits and $R = 1/2$                                                       | 64 |

| 3.7  | EMS for a $GF(64)$ -code and two cluster-code with $p_1 = 3, 4, p_2 = 6$ ,    |    |

|      | N = 3000-bits and $R = 1/2$                                                   | 64 |

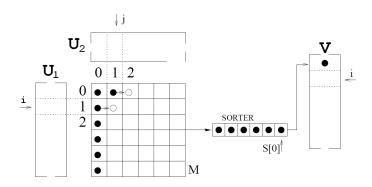

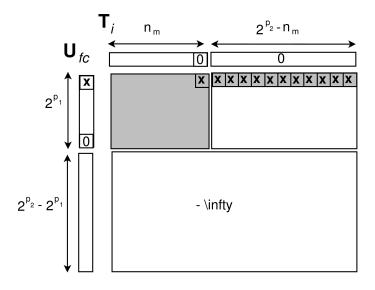

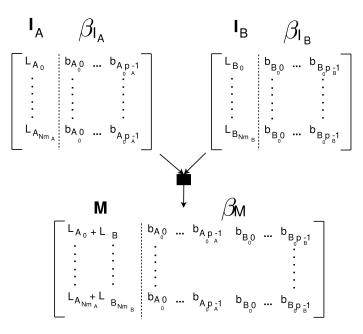

| 3.8  | The matrix $M$ formed with full-size input vectors $U_{fc}$ and $T_j$         | 67 |

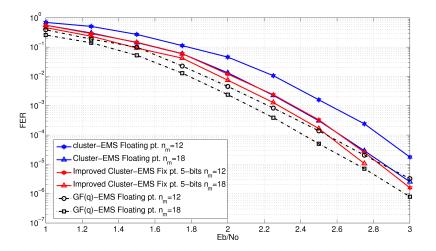

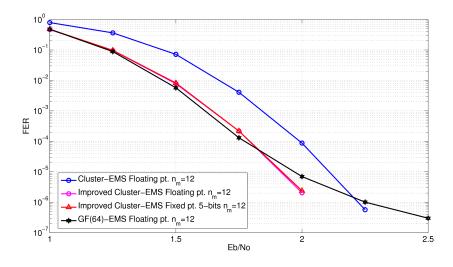

| 3.9  | Improved EMS for a cluster-code with $p_1 = 4$ , $p_2 = 6$ , $N = 576$ -bits  |    |

|      | and $R = 1/2$                                                                 | 68 |

| 3.10 | Improved EMS for a cluster-code with $p_1 = 4$ , $p_2 = 6$ , $N = 2304$ -bits |    |

|      | and $R = 1/2$                                                                 | 69 |

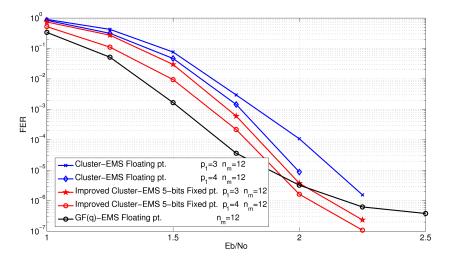

| 3.11 | Improved EMS for two cluster-codes with $p_1 = 3, 4, p_2 = 6, N =$            |    |

|      | 3000-bits and $R = 1/2$                                                       | 70 |

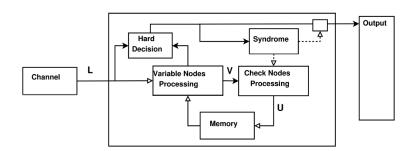

| 3.12 | The main components of the decoder                                            | 71 |

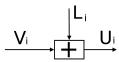

| 3.13                                                      | Variable update processor                                                                                                                                                                                                                                                                                                            | 72                   |

|-----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 3.14                                                      | Improved EMS for two cluster-codes with $p_1 = 3, 4, p_2 = 6, N =$                                                                                                                                                                                                                                                                   |                      |

|                                                           | 3000-bits and $R = 1/2$                                                                                                                                                                                                                                                                                                              | 73                   |

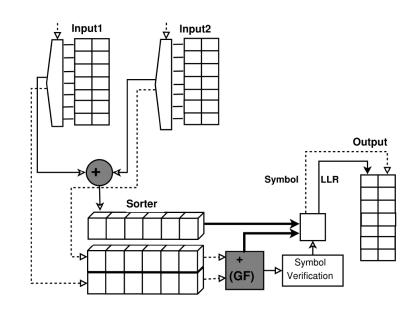

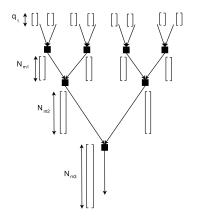

| 3.15                                                      | Multiple instances of a check update process scrambled in parallel us-                                                                                                                                                                                                                                                               |                      |

|                                                           | ing diversity of group-LDPC codes                                                                                                                                                                                                                                                                                                    | 76                   |

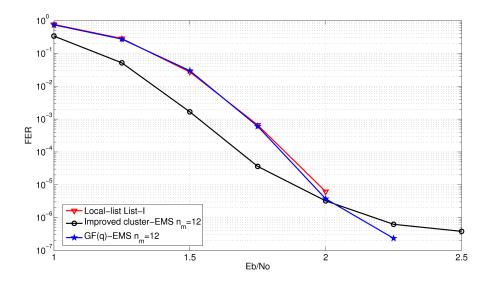

| 3.16                                                      | Decoder diversity $N = 3000, R = 0.5, (p_1, p_2) = (3, 6)$                                                                                                                                                                                                                                                                           | 78                   |

| 3.17                                                      | Decoder diversity $N = 3000, R = 0.5, (p_1, p_2) = (4, 6)$                                                                                                                                                                                                                                                                           | 78                   |

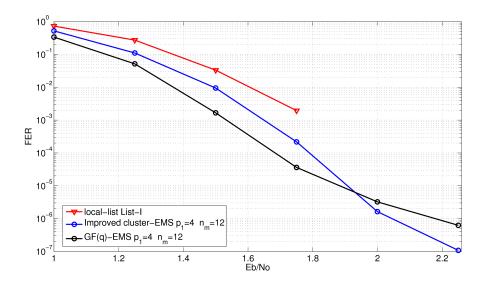

| 3.18                                                      | Decoder diversity $N = 4800, R = 0.88, (p_1, p_2) = (3, 7) \dots$                                                                                                                                                                                                                                                                    | 79                   |

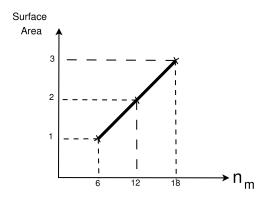

| 3.19                                                      | Normalized area vs. number of parallel check-update processes                                                                                                                                                                                                                                                                        | 80                   |

| 3.20                                                      | Normalized area vs. message truncation value $n_m$                                                                                                                                                                                                                                                                                   | 81                   |

| 4.1                                                       | A trallic for an order 64 sheet node of degree $d = 6$                                                                                                                                                                                                                                                                               |                      |

| т. 1                                                      | A trellis for an order-64 check node of degree $d_c = 6$                                                                                                                                                                                                                                                                             | 84                   |

| 4.2                                                       | A trends for an order-04 check hode of degree $a_c = 0$                                                                                                                                                                                                                                                                              | 84<br>85             |

|                                                           |                                                                                                                                                                                                                                                                                                                                      |                      |

| 4.2                                                       | A list of codewords and their likelihoods                                                                                                                                                                                                                                                                                            | 85                   |

| 4.2<br>4.3                                                | A list of codewords and their likelihoods                                                                                                                                                                                                                                                                                            | 85<br>86             |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>             | A list of codewords and their likelihoods                                                                                                                                                                                                                                                                                            | 85<br>86             |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>             | A list of codewords and their likelihoods $\dots \dots \dots \dots \dots \dots$<br>Tree for creation of list $\dots \dots \dots$<br>Elementary step of the tree $\dots \dots $ | 85<br>86<br>87       |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>4.5</li></ul> | A list of codewords and their likelihoods                                                                                                                                                                                                                                                                                            | 85<br>86<br>87       |

| <ul><li>4.2</li><li>4.3</li><li>4.4</li><li>4.5</li></ul> | A list of codewords and their likelihoods                                                                                                                                                                                                                                                                                            | 85<br>86<br>87<br>92 |

# **List of Tables**

| 2.1 | Primitive Polynomials                                                     | 9  |

|-----|---------------------------------------------------------------------------|----|

| 2.2 | Binary and Polynomial representation of Finite Field $GF(8)$              | 10 |

| 2.3 | Computational complexity of the BP algorithm                              | 20 |

| 2.4 | Memory required to store messages in a NB-Tanner Graph                    | 33 |

| 2.5 | Vote values for the symbol flipping decoding for generalized LDPC         |    |

|     | based on 2-super codes                                                    | 48 |

| 2.6 | Number of operations required for an elementary process of a variable     |    |

|     | node                                                                      | 52 |

| 2.7 | Number of operations required for an elementary process of a check        |    |

|     | node                                                                      | 53 |

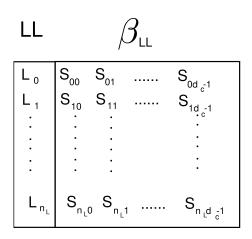

| 3.1 | Size of LLR-vectors                                                       | 74 |

| 3.2 | Number of operations at a variable node with $d_v = 2$                    | 74 |

| 3.3 | Number of operations at a check node                                      | 75 |

| 4.1 | Number of operations required to process the check nodes                  | 91 |

| 4.2 | List size and no. of operations for the code with $d_c = 8$ and $p_1 = 3$ | 91 |

| 4.3 | List size and no. of operations for the code with $d_c = 6$ and $p_1 = 4$ | 92 |

# **Abbreviations**

| APP     | A-posteriori probability                             |

|---------|------------------------------------------------------|

| AWGN    | Added White Gaussian Noise                           |

| BER     | Bit Error Rate                                       |

| BIAWGN  | Binary Input Additive White Gaussian Noise (channel) |

| BP      | Belief Propagation                                   |

| ECC     | Error Correcting Codes                               |

| EMS     | Extended Min-Sum                                     |

| FER     | Frame Error Rate                                     |

| FFT     | Fast Fourier Transform                               |

| FPGA    | Field Programmable Gate Arrays                       |

| FT      | Fourier Transform                                    |

| GF      | Galois Field                                         |

| HDD     | Hard Decision Decoder                                |

| ISI     | Inter Symbol Interference                            |

| LDPC    | Low Density Parity Check (code)                      |

| LUT     | Look-up table                                        |

| ML      | Maximum Likelihood                                   |

| MPA     | Message Passing Algorithm                            |

| MSA     | Min-Sum Algorithm                                    |

| NB-LDPC | Non-binary Low Density Parity Check                  |

| PCM     | Parity Check Matrix                                  |

| PDF     | Probability Density Function                         |

| SNR     | Signal-to-Noise Ratio                                |

| SPA     | Sum Product Algorithm                                |

## Introduction - Context and Background

### 1.1 Context and background

N this thesis we present our work in the domain of error correction codes (ECC), which makes possible the transmission of data over imperfect channels with the least possible errors. In this chapter we introduce the basic concepts explored in the thesis. We discuss the imporantance of LDPC codes in communication systems and the interest of using non-binary LDPC codes over their binary counterparts which is the main motivation behind this work.

### 1.1.1 Introduction

Figure 1.1 depicts the block diagram of a traditional communication system. The transmitter and receiver are the two entities communicating with each other whilst the channel adds imperfection to the transmission. The transmitter is composed of mainly three elements: source and channel encoders and a modulator. Similarly, at the receiver there is the de-modulator and the two decoders. The source encoder removes redundancy in the data received from the source, thus compressing the data. This helps in increasing the data rate of the transmitter. On the other hand, the channel encoder adds redundancy to the data received from the source encoder. This helps in making the data robust to the errors introduced by the channel. The ratio of the information data and the transmitted data forms the coding-rate  $\mathbf{R}$  of the code, which is a parameter of the coding system. The modulator modulates the data as per the type and order of modulation installed. The channel adds degradation into the transmitted data. This includes ambiant noise generally modeled as additive white gaussian noise (AWGN), inter-symbol interference (ISI) due to multi-path fading and multi-user interference in multi-user systems.

The AWGN transmission channel is generally modeled as noise b with zero mean and variance  $\sigma^2$ ,  $(\mathcal{N}(0, \sigma^2))$ . Consider a transmitted finite energy signal x. The received signal is then modelled as y = x + b. This transmission defines a gaussian channel characterized by the ratio of the signal energy and energy of noise  $E_b/N_0$ .

Figure 1.1: Block Diagram of a communication system

At the receiver, the demodulator converts the modulated signal into bit streams. The channel decoder applies an error correcting procedure to correct the errors introduced by the channel. The source encoder then decompresses the received information and reconstructs the transmitted data.

The principle of error correcting codes is to add redundancy to the data to be transmitted and then use this redundancy to re-create the data after it has been distorted by the channel. The channel encoder encodes a message of K bits to a codeword of N bits. The K bits are called as the information bits whereas the M = N - K redundant bits are called as the parity bits. The ratio R = K/N is called the rate of the code.

$$\{0,1\}^K \Rightarrow \mathcal{C} \subseteq \{0,1\}^N \tag{1.1}$$

Error correction methods consist in finding the codeword having the smallest distance with the received signal. The capacity of an error correcting code is measured as the minimum distance  $d_{min}$  of the code, which is the smallest distance between two elements of the codeword set C. If the received signal has a distance greater than  $d_{min}/2$ from the transmitted codeword, there is a possibility that the codeword nearest to the received signal is not the codeword which was initially transmitted. Therefore  $d_{min}$ plays an important role in terms of the error correcting capability of a code. From a geometrical point of view, the codewords form hyper-spheres of radius  $d_{min}/2$  in a N-dimensional space. If the received signal is outside the sphere, the probability of decoding a wrong codeword increases.

The decoding procedure is thus an algorithmic problem in which we search the nearest codeword to the received signal in a multidimensional space. The optimal solution is thus an extensive sequential search of the nearest codeword which can make the decoding procedure quite complex i.e. of the order  $O(2^K)$ . Thus various sub-optimal but faster solutions were proposed.

### 1.1.2 History

In 1948, Claude E. Shannon laid the mathematical foundation of modern information theory and gave the very first systematic framework for communication in his landmark paper [Sha48]. He introduced the concept of redundant channel coding as a method to achieve reliable communication on a noisy channel with known capacity. In particular, he proved that for sufficiently long codes arbitrarily reliable communication is possible at any coding rate below the capacity. Since then, the challenge of channel coding has been to design practical coding solutions that approach the channel capacity.

During the following decades, a lot of coding families were invented e.g. Hamming codes, Golay codes, Reed-Muller codes, convolutional codes, BCH codes, Reed-Solomon codes are just a few to mention. The goal was to construct codes with good properties and to find low complexity algorithms which are able to perform near optimum decoding for these codes. In 1993, Turbo codes [BGT93] were discovered which proved to be a major breakthrough for reliable communication through noisy channels. A practical coding scheme was presented that approaches the channel capacity within 1 dB at a bit error rate (BER) of  $10^{-6}$ . More importantly it showed the potential of iterative decoding as a mean of approaching the channel capacity. Since then, there has been a tremendous amount of research on codes that are iteratively decodable and generally defined by graphs.

Low-Density Parity-Check (LDPC) codes were originally presented by Gallager [Gal62] in 1963, but received little attention at that time. The large computational needs for the decoding of long LDPC codes prevented their widespread use until major advances were made in computing, which eventually allowed cost-effective decoding implementation. With the breakthrough of turbo codes, they were rediscovered [Mac97] and regained more attention. However, one noticable and important exception is the work of Tanner [Tan81], in 1981, in which he generalized LDPC codes and introduced a graphical representation of LDPC codes, called as Tanner graph. Tanner graphs of LDPC codes are bipartite graphs that contains two types of nodes which are connected via edges. They are called the variable and check nodes representing the symbols and the parities respectively.

More recently, binary LDPC codes were considered in standards like DVB-S2, WI-MAX, DSL, W-LAN etc. However, they start to show their weakness when the code size is small or moderate and when higher order modulation is used for transmission. Non-binary LDPC (NB-LDPC) codes were proposed [DM98] and they showed better

performance for codes of smaller length and defined in higher field orders. NB-LDPC codes then became candidates for future communication systems.

There are three aspects related to the design of a good channel decoder: its performance, the technology and its usage. The performance aspect plays an important role towards the quality of transmission. From a technological point of view, the decoding algorithm is generally composed of heavy computations and it must be capable of performing these computations with the least latency and highest data rate. This makes it necessary to envisage the decoding algorithm with a reduced complexity of implementation. Hence, in order to realize the hardware implementation of the decoder, we have to make a compromise between performance and complexity. On the other hand, digital communication systems are being increasingly used in the daily lives of the general public (mobile phones, digital TVs, PDAs, GPS etc.). More and more devices are being introduced and the number of communicating devices has increased. This results in the evolution of the use of technology and thus has two consequences. Firstly, there is a direct impact on the consumption characteristics and secondly the flexibility necessary to adapt the devices to different standards and technologies. Alongside, the prices of the circuits manufacturing must also be controlled.

## 1.2 Motivation and objective of the thesis

Binary-LDPC codes are based on the verification of parities of a matrix using for decoding, called the parity check matrix (PCM). The PCM has a very low density of ones, such that as the size of the matrix tends to infinite, the ratio of the non-zero elements to the null elements tends to zero [Rya03]. Non-binary-LDPC codes are a direct generalization of the binary case and the non-zero elements of the PCM are then defined in a Galois field, denoted as GF(q). The NB-PCM is a low density matrix and it is represented by the bipartite Tanner graph.

It is widely accepted that the degradation in performance of an LDPC decoder comes due to dependance of the messages passed betweeen the nodes of the Tanner graph. This dependance is induced because of the topological structure of the code which includes cycles, stopping and trapping sets. This dependance is even more enhanced when the messages used to initialize the decoder are already correlated by the channel. NB-LDPC codes help in reducing the dependance of the messages for the following main reasons:

• For the same code-rate and binary-length, the graph corresponding to a NB-LDPC codes is typically less dense as compared to the graph corresponding to the a binary-LDPC code [MD99]. As a consequence, the graph corresponding

to the NB-LDPC code has better topological properties i.e. larger girth and less stopping and trapping sets.

For a binary LDPC code transmitted with a high order modulation, the Maximum a-posteriori (MAP) demapper creates probabilities at the binary level for the decoder. This implies that decoder input messages are correlated even in the absence of cycles. However, if the LDPC code is defined in the same or higher order of Galois field as the order of modulation, the NB-LDPC decoder is initialized with non-correlated messages. Therefore, NB-LDPC codes perform better for high order modulation [SF02].

However, the advantages of using NB-LDPC codes come with the consequence of an heavily increased decoding complexity. For a code defined in GF(q), the complexity is of the order  $O(q^2)$  [WSM04a]. Similarly, the memory required for storing messages is of order O(q). Consequently, the implementation of an LDPC-decoder defined over a field order q > 64 becomes practically impossible.

The main objective of the thesis is to develop a reduced complexity algorithm for non-binary LDPC codes that exhibit excellent performance together with an efficient parallel implementation. For better decoding performance, not only the decoding algorithm is important, but also the structure of the code plays an important role. With this goal, NB-LDPC codes defined over finite groups were proposed [CPD<sup>+</sup>09]. A special case of group-LDPC codes is when the variable nodes are processed in a smaller group-order as compared to the check nodes. We refer to this family of codes as NB cluster-LDPC codes. They are designed to have a higher minimum distance and are foreseen to be good candidates for high rate applications. For this reason, we have concentrated our work on this family of codes and we propose decoding algorithms for NB cluster-LDPC codes.

## 1.3 Thesis organization

In chapter 2, we explain the basics of non-binary LDPC codes. In the first part of the chapter, we explain the graphical and matrix representation of non-binary LDPC defined over finite Galois fields and their generalization to finite groups. We then introduce the concept of clusters-LDPC codes defined over finite groups. In the second part of the chapter, we present a detailed and state of the art description of various non-binary LDPC decoders proposed in literature. In the third and last part of the chapter, we make a comparison between the complexities of various decoders.

In chapter 3, we present the generalization of the EMS algorithm to NB cluster-LDPC codes. We refer to it as the cluster-EMS algorithm. In the second part of the chapter,

we propose some improvements in the decoding procedure to adapt the EMS algorithm to cluster-codes in a better manner. We also present a hardware architecture for our proposed improved cluster-EMS algorithm and compare its complexity to other algorithms. In the third part of the chapter, we then propose a method to reduce the surface area of the decoder. The method is based on the implementation of several instances of a check update process in parallel with a very low complexity and then fusioning the output of each instance to compute the extrinsic output of the check node. We also analyse the effect on the area of the decoder.

In chapter 4, we explain our second proposed decoder which is based on the concept of list decoding. The decoding algorithm is based on the creation of lists based on local parities at the check nodes level and therefore, we call it local-list decoder. In the second part of the chapter, we propose an idea to reduce the complexity of the local-list decoder, but our proposed idea was not supported by Monte-Carlo simulations. However, for the sake of information, we explain the idea.

In chapter 5, we conclude the manuscript and present the summary and perspectives of the work.

## Non-binary LDPC codes

THIS chapter presents the background and state of the art information about nonbinary LDPC codes. In the first part of the chapter, we present the structure and representation of the various families of LDPC codes. We start by introducing NB-LDPC codes defined over finite Galois fields and explain the Belief-Propagation (BP) algorithm used for decoding. After that, we move towards NB-LDPC codes defined over groups and emphasize on a special case of NB-LDPC codes defined over finite groups which we term as cluster NB-LDPC codes. In the second part of the chapter, we introduce various low complexity decoding algorithms that have been proposed in the literature. As a conclusion to the chapter, we make a comparison between the decoding complexity and performance for some of these algorithms.

## 2.1 Classification of Non-binary LDPC codes

Low density Parity check codes (LDPC) are a class of linear block codes that uses a generator matrix for encoding and a parity check matrix (PCM) for decoding. The name low density parity check comes from the fact that the PCM has a very low density of non-zero elements as compared to the number of zero elements. By definition, the PCM ratio between the number of non-zero elements and the number of zero elements tends to zero as the size of the matrix tends to infinity. The PCM is represented in the form of a Tanner graph which is a bipartite graph with two types of nodes. This facilitates the use of an iterative decoding algorithm where messages are being passed between the two sets of nodes. The messages represent in some sense *reliabilities* of the symbol values. The decoder operates in an iterative fashion, and A-posteriori probabilities (APP) are calculated at the end of each iteration to make a decision on the received symbols.

We first explain the structure and decoding of codes defined over finite Galois fields and then detail the concept of LDPC codes defined over finite groups. We then explain an interesting family of codes which we call cluster-LDPC codes.

#### 2.1 Classification of Non-binary LDPC codes

| p | Primitive Polynomials                                                            |

|---|----------------------------------------------------------------------------------|

| 1 | 1+x                                                                              |

| 2 | $1 + x + x^2$                                                                    |

| 3 | $1 + x + x^3, 1 + x^2 + x^3$                                                     |

| 4 | $1 + x + x^4, 1 + x^3 + x^4$                                                     |

| 5 | $1 + x^2 + x^5, 1 + x + x^2 + x^3, x^5, 1 + x^3 + x^5, 1 + x + x^3 + x^4 + x^5,$ |

|   | $1 + x^2 + x^3 + x^4 + x^5, 1 + x + x^2 + x^4 + x^5$                             |

Table 2.1: Primitive Polynomials

### 2.1.1 NB-LDPC codes defined on finite Galois fields

#### Galois Fields

A Galois field is a finite field with a finite order, which is either a prime number or the power of a prime number. A field of order  $n^p = q$  is represented as  $GF(n^p)$  or GF(q) and it contains q-elements which are denoted as  $\{0, 1, \alpha, \alpha^2, ..., \alpha^{q-2}\}$  respectively. A specific type called as *characteristic-2* fields are the fields when n = 2. All the elements of a *characteristic-2* field can be represented in a polynomial format [PFD06a]. The primitive polynomial of the field is defined to be an irreducible polynomial that generates all the other polynomials. As a result, the symbol represented by the primitive polynomial is called as the primitive symbol  $\alpha$  of the field  $GF(2^p)$ , there exists a primitive polynomial of degree p over GF(q) [PFD06b]. Table 2.1 lists the primitive polynomials for p equals 1 through 5. We can be observe that for p = 1, the field is a binary field and for  $p \ge 2$ , it represents a non-binary field. Binary LDPC codes are defined over a Galois field GF(2), with  $\{0, 1\}$  being the field elements. Hence non-binary LDPC codes can be considered as a direct generalization of binary LDPC codes.

Each element of a *characteristic-2* field is represented by a polynomial with binary coefficients. Table 2.2 shows the example for p = 3 while considering the primitive polynomial  $1 + x + x^3$ . The field consists of 8 elements and each one has a binary representation composed of the binary coefficients of the associated polynomial. With this representation finite field addition and multiplication becomes polynomial addition and multiplication, where the addition is modulo-2. We will see later in the chapter that the PCM of a non-binary LDPC code can also be represented in a binary matrix form using the binary coefficients of the polynomial representation.

| Element    | Binary Rep. | Polynomial Sum          |

|------------|-------------|-------------------------|

| 0          | 000         | 0                       |

| $\alpha^0$ | 100         | 1                       |

| $\alpha^1$ | 010         | α                       |

| $\alpha^2$ | 001         | $\alpha^2$              |

| $\alpha^3$ | 110         | $\alpha + 1$            |

| $\alpha^4$ | 011         | $\alpha^2 + \alpha$     |

| $\alpha^5$ | 111         | $\alpha^2 + \alpha + 1$ |

| $\alpha^6$ | 101         | $\alpha^2 + 1$          |

Table 2.2: Binary and Polynomial representation of Finite Field GF(8)

#### The parity check matrix

An LDPC block code defined over a finite Galois field  $GF(2^p)$  is described as a *K*-dimensional subspace C of the vector space  $GF(2^p)^N$  of *N*-tuples. Hence the code C has a total of  $(2^p)^K$  codewords. The code C is a subspace and is spanned by the basis:

$$\mathbb{G} = \{g_0, g_1, \dots, g_{K-1}\}$$

(2.1)

Each codeword  $c \in C$  is then written as:

$$c = u_0 g_0 + u_1 g_1 + \dots + u_{K-1} g_{K-1}$$

(2.2)

for any vector  $\{u_i\}$ . In matrix form, this equation can be written as  $c = \mathbf{u}.G$  where  $\mathbf{u} = [u_0, u_1, ..., u_{K-1}]$  and G is the  $(K \times N)$  generator matrix whose rows are the vectors  $\{g_i\}$  of the basis.

$$C = \{c = u.G, \forall u \in GF(2^p)^K\}$$

(2.3)

The M = (N-K) dimensional dual space  $\mathcal{C}^{\perp}$  of  $\mathcal{C}$  comprises of vectors  $x \in GF(2^p)^N$  for which  $x\mathcal{C}^{\perp} = 0$ . The basis of  $\mathcal{C}^{\perp}$  is represented as:

$$\mathbb{H}^{\perp} = \{h_0, h_1, \dots, h_{M-1}\}$$

(2.4)

Therefore, this implies that:

$$C^{\perp} = \{ c \in GF(2^p)^N : H.c \stackrel{GF(2^p)}{=} 0 \}$$

(2.5)

where H is a  $(M \times N)$  matrix whose rows are the  $\{h_i\}$  elements of the basis. It is the generator matrix of the dual space  $C^{\perp}$  and is called as the parity check matrix (PCM) of the code C. The rows of H can also be seen as the coefficients of a linear equa-

tion system. Each equation is called as a parity check equation as it performs the test whether the received word verifies the parity. There are M = N - K such tests and it gives the name parity check matrix (PCM). The PCM for a  $(10 \times 5)$  LDPC code is shown in Fig. 2.1.

Figure 2.1: A non-binary LDPC parity check matrix

The original PCM proposed by Gallager had equal number of non-zero elements in all rows and columns,  $d_c$  and  $d_v$  respectively. Such type of a code is called as a regular LDPC code. However a code with a different number of non-zero elements in its rows and columns is termed irregular LDPC codes.

Using the generator matrix G, for a frame of length K, the encoders create a codeword of length N, where N - K are the redundant symbols. The rate of the code can be defined as:

$$R = \frac{K}{N} \tag{2.6}$$

The rate of a code helps in determining the data-rate of the communication system as it defines the total number information sent versus the redundancy added to the transmission.

#### The Tanner graph representation

In 1981, Tanner presented a bipartite graphical representation of binary LDPC codes which is called as a Tanner graph after his name [Tan81]. A graph is called bipartite if it has two disjoint sets of nodes which are connected via edges and no two edges of the same set are connected to each other. The two sets of nodes represent the variables and the functions between them respectively. In the case of LDPC codes, the variables are the symbols of the codeword and are thus called as variable nodes. The functions between the variables correspond to the parity check equations and thus, these nodes are called as parity check nodes.

Consider a  $(M \times N)$  regular-LDPC code, with  $d_v$  and  $d_c$  non-zero elements in the PCM at each column and row respectively. The Tanner graph is constructed by associating a variable node to each column and a parity node to each row of the PCM.

There are M parity check nodes and N variable nodes. For each non-zero element  $h_{ij}$ , an edge is created between the  $i^{th}$  parity node and the  $j^{th}$  variable node. This way each parity node is connected to  $d_c$  variable nodes and likewise each variable node is connected to  $d_v$  parity check nodes.  $d_c$  and  $d_v$  are termed as the degree of connection of the check and variable nodes respectively.

Figure 2.2: The Tanner Graph for a non-binary parity check matrix

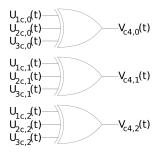

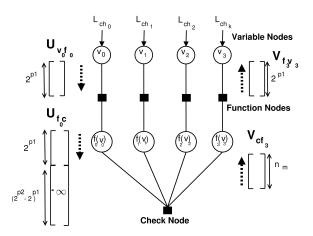

When the non-zero elements  $h_{ij}$  are the elements of a non-binary finite field GF(q), we add another class of node called as the function nodes [DF07]. These nodes correspond to multiplication of the codeword symbols with the non-zero elements  $h_{ij} \in GF(q)$ . After multiplication, the messages at the check nodes input become independent of the non-binary values of the PCM and they can be processed concurrently. Fig. 2.2 represents the Tanner graph for the PCM of Fig. 2.1 with (M, N) = (5, 10) and  $(d_c, d_v) = (4, 2)$ .

The function node models the multiplication of the symbols  $c_j$  and the non-zero elements  $h_j$  by a cyclic permutation of the message values [DF07] and this is why they are also referred as permutation nodes. A cyclic permutation of a message  $U_{vp}$  is shown in Fig. 2.3. The LLR value of the symbol 0 remains at the same index and all the other values are shifted in a cyclic fashion by  $\alpha^3$ .

A *cycle* in a Tanner graph is represented by a path that finishes at the same node from where it had emerged. The shortest cycle of a graph is called as its *girth*. The smallest possible girth of an LDPC code is 4. This is because the Tanner graph is a bipartite graph where two similar types of nodes do not interconnect directly. Cycles bring in dependance between the transmitted which as a consequence degrades the decoding performance of the code. Therefore, it is desirable to avoid cycles, specially short length cycles.

Figure 2.3: A cyclic permutation of a message at the permutation node

### The binary representation of the non-binary PCM

When the field order of a NB-LDPC code is a power of 2, the non-binary elements of the field have a polynomial representation [PFD06b], which in turn provides a binary representation of the field elements.

Consider a  $(M \times N)$  regular NB-LDPC code defined in a Galois field GF(q), with  $q = 2^p$  as the order of the field. The degrees of connection of the variable and check nodes are  $(d_v, d_c)$  respectively. The non-binary parity check matrix H associated to the code has its non-zero elements belonging to the Galois field  $GF(2^p = q)$ . The non-zero elements belong to the set  $S = \{\alpha^i : i = 0, ..., q - 2\}$ , with  $\alpha$  being the primitive element of the field. We define a primitive polynomial of degree p for the field.

$$p(x) = a_0 + a_1 x + a_2 x^2 \dots + x^p$$

(2.7)

A companion matrix A of size  $p \times p$  is also associated to the primitive polynomial [PFD06a].

|            | 0     | 1     | 0     | 0     | <br>0                                                               |

|------------|-------|-------|-------|-------|---------------------------------------------------------------------|

|            | 0     | 0     | 1     | 0     | <br>0                                                               |

| 1 _        | 0     | 0     | 0     | 1     | <br>0                                                               |

| $A \equiv$ | .     |       | •     | •     |                                                                     |

|            | 0     |       |       |       | <br>1                                                               |

|            | $a_0$ | $a_1$ | $a_2$ | $a_3$ | <br>$\begin{array}{c} 0 \\ 0 \\ 0 \\ . \\ 1 \\ a_{p-1} \end{array}$ |

where  $[a_0, ..., a_{p-1}]$  are the coefficients of the primitive polynomial p(x).

Since p(x) is the primitive polynomial of the field  $GF(2^p)$ , A is called as its primitive element under matrix representation. As a result, the powers of the matrix A generate the binary matrix representations of all the other elements of the field. Thus the non-zero elements  $h_{ij}$  of the PCM can be written in the form of a  $(p \times p)$  binary matrices  $H_{ij}$ , where  $H_{ij}$  is the result of the transpose of a power of the primitive matrix of the Galois field. Subsequently, the  $(M \times N)$  NB-PCM can be written in the form of a  $M_b \times N_b$  binary PCM, where  $M_b = pM$  and  $N_b = pN$  as shown in Fig. 2.4. The zero elements of the PCM are represented with all-zero matrices of size  $(p \times p)$ .

|                |     | ← p=4 → |      |      |      |      |      |

|----------------|-----|---------|------|------|------|------|------|

|                | ↑   | 0001    | 0000 | 0110 | 0000 | 0011 | 0000 |

| $H_{_{bin}} =$ | p=4 | 1001    | 0000 | 0101 | 0000 | 1010 | 0000 |

|                |     | 0100    | 0000 | 1010 | 0000 | 1101 | 0000 |

|                |     | 0010    | 0000 | 1101 | 0000 | 0110 | 0000 |

|                |     | 0000    | 1111 | 0000 | 0000 | 0000 | 0100 |

|                |     | 0000    | 1000 | 0000 | 0000 | 0000 | 0110 |

|                |     | 0000    | 1100 | 0000 | 0000 | 0000 | 0011 |

|                |     | 0000    | 1110 | 0000 | 0000 | 0000 | 1001 |

|                |     | 0000    | 0011 | 0000 | 0101 | 0000 | 0000 |

|                |     | 0000    | 1010 | 0000 | 1111 | 0000 | 0000 |

|                |     | 0000    | 1101 | 0000 | 0111 | 0000 | 0000 |

|                |     | 0000    | 0110 | 0000 | 1011 | 0000 | 0000 |

Figure 2.4: Binary representation of a GF(q)-LDPC code

The arithmetics on the GF(q) elements are carried out using modulo-2 addition and multiplication of the polynomial representations. Similarly, the arithmetics on the matrix representation can be carried out using modulo-2 arithmetics over the matrix representations. The parity check equation can, thus, be written in the vectorial domain as:

$$\sum_{j:H_{ij}\neq 0} H_{ij}X_j^T = 0^T$$

(2.8)

where  $H_{ij}$  is the matrix representation of the Galois field element  $h_{ij}$ ,  $X_j$  is the *p*-bits binary mapping of the symbol  $c_j$  and 0 is the all zero component vector.

As described earlier that the function nodes are added to a NB-Tanner graph which makes the check nodes independant of the non-binary elements of the PCM. The function nodes realize the multiplication of the messages with the non-binary elements by a cyclic permutation of the message values. For a function node bearing the value  $h_{ij}$ , the message values are shifted in a cyclic fashion by a value  $h_{ij}$ . The cyclic permutation of the message values can be obtained using the binary matrix representation  $H_{ij}$ of  $h_{ij}$  and the *p*-bits binary mapping  $\{b_{\alpha i}[k]\}_{k=0,\dots,p-1}$  of the symbols  $\alpha^i \in GF(q)$ . The multiplication of the matrix  $H_{ij}$  with  $b_{\alpha i}$  results in the binary mapping of another element  $\alpha^j$ , where  $(\alpha^i, \alpha^j) \in GF(q)$ .

$$b_{\alpha^j} = H_{ij}.b_{\alpha^i} \tag{2.9}$$

This multiplication of subsequent elements are followed in a cyclic fashion and thus it results in a cyclic permutation of the message values as shown in Fig. 2.3.

#### The Belief propagation decoding algorithm

Gallager proposed a quasi-optimal decoding algorithm for binary LDPC codes which is termed Belief propagation (BP) [Gal62]. It is an iterative message passing algorithm which is also called as the Sum-Product algorithm (SPA). As the name belief propagation suggests, the algorithm is based on the propagation of messages composed of the probabilities of the symbols  $c_n$ . To each edge of the Tanner graph, two messages are associated for the two directions of propagation i.e. one from the variable nodes to the check nodes and the other in the reverse direction.

The algorithms used for the decoding of binary LDPC codes can also be generalised to non-binary LDPC codes defined over finite fields by employing the various operations in correspondance to finite fields. MacKay et al. generalised the belief propagation algorithm to non-binary LDPC codes defined over finite fields [DM98]. The messages flowing through the graph are of size q and they represent the probabilities of the symbols  $c_n$ , when the code is defined in a finite field GF(q). For example, a message vector associated to a random variable z is written as:

$$P(z) = [P[0] \ P[1] \ P[\alpha] \ \dots \ P[\alpha^{q-2}]]$$

(2.10)

where  $P[\alpha^i] = P(z = \alpha^i)$  represents the probability of the random variable z being equal to  $\alpha^i \in GF(q)$ .

The Tanner graph is processed in two steps:

- 1. First the variable nodes processes the inputs by a term by term multiplication of the  $d_v 1$  input messages to calculate the extrinsic outputs of the variable nodes.

- 2. The second steps involves the computation of the extrinsic outputs of the parity nodes while verifying the parity equations at each check node.

The  $i^{th}$ -parity equation is written as:

$$\sum_{j=0}^{d_c-1} h_{ij} \otimes c_j = 0$$

(2.11)

where  $h_{ij}$  are the non-zero elements of the  $i^{th}$  row of the parity matrix H,  $c_j$  are the symbols of the codeword that participate in the parity and  $d_c$  is the degree of connection of the check node. The messages circulating between the nodes contain extrinsic information. This means that for any edge j on a node of degree d, the output on the edge j is calculated as a function of all the other inputs excluding the input message from edge j itself. This holds for both, the variable and check nodes.

The Belief propagation (BP) algorithm is based on the computation of the a-posteriori probability of the codeword symbols. For a transmitted codeword  $c = [c_0c_1...c_{N-1}]$ , we are interested in computing the aposteriori probability (APP) of a given symbol  $\alpha^j$  of a word  $c_i$  with in the transmitted codeword, given the received word  $y = [y_0y_1...y_{N-1}]$ .

$$P(c_i = \alpha^j | y) \tag{2.12}$$

For the messages that traverse the Tanner graph, we use the representation as follows: U is a message flowing from the variable nodes towards the check node and V is a message in the reverse direction. Thus,  $\{V_{piv}\}_{i=0...d_v-1}$  is the set of messages entering a variable node v of degree  $d_v$  and  $\{U_{vp_i}\}_{i=0...d_v-1}$  is the set of output messages of the same variable node. The index  $p_i v$  indicates the direction of propagation of the message i.e. from the permutation node  $p_i$  to the variable node v and  $vp_i$  in the reverse direction. Similarly, the sets  $\{U_{pic}\}_{i=0...d_c-1}$  and  $\{V_{cp_i}\}_{i=0...d_c-1}$  are the set of inputs and outputs of the check node c of degree  $d_c$ . Fig. 2.5 represents the Tanner graph of a single parity check and denotes the various messages traversing though the graph.

Figure 2.5: The messages flowing across a Tanner graph for the BP algorithm

The Belief Propagation (BP) algorithm is composed of six steps:

#### 1 - Initialization:

During this step, all the messages U are initialized with the likelihood information

from the channel.

$$U_{vp_i}[0 \dots \alpha^{q-2}] = [P_{ch_v}[0] P_{ch_v}[1] \dots P_{ch_v}[\alpha^{q-2}]] , \quad v = 0, \dots, N-1$$

(2.13)

where  $\{0, 1, ..., \alpha^{q-2}\} \in GF(q)$  are the elements of the field and:

$$P_{ch_v}[\alpha^i] = P(y_v|c_v = \alpha^i)$$

(2.14)

is the likelihood probability of the symbol  $\alpha^i$  information calculated at the channel output.

#### 2 - Variable nodes processing:

Consider a variable node v of degree  $d_v$  with the input messages  $\{V_{p_kv}\}_{k=0...d_v-1}$  as shown in Fig.2.6. To calculate the output messages  $U_{vp_k}$  on the edge k, we consider all the input messages except for the input message on the edge k.

$$U_{vp_{k}}[\alpha^{i}] = \mu_{vp_{k}} P_{ch_{v}}[\alpha^{i}] \prod_{j=0, j \neq k}^{d_{v}-1} V_{p_{j}v}[\alpha^{i}]$$

(2.15)

where  $\alpha^i \in GF(q), k = 0, ..., d_v - 1$  and  $\mu_{vp_k}$  is a normalization factor such that:

$$\sum_{i=0}^{q-1} U_{vp_k}[\alpha^i] = 1$$

(2.16)

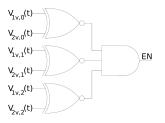

Figure 2.6: The degree  $d_v$  variable node update

#### **3 - Cyclic-permutation nodes processing:**

These nodes multiply the codeword elements with the non-binary elements  $h_p$  of the PCM. Since Finite Galois fields are cyclic and multiplication in GF(q) correspond to a cyclic permutation of the message values [DF07]. The message  $U_{vp}$  from the variable

node v is udpated by the permutation node p carrying a value  $h_p$ , to a message  $U_{pc}$  as:

$$U_{pc}[0...\alpha^{q-2}] = \Psi_{h_p} U_{vp}[0...\alpha^{q-2}]$$

(2.17)

where  $\Psi_{h_p}$  is the  $(q \times q)$  permutation matrix that corresponds to the non-binary value  $h_p$ . All the values of the message are circularly shifted except for the value labelled by the symbol 0, which remains at its place. The permutation process is expressed as:

$$U_{pc}[h_p \otimes \alpha^i] = U_{vp}[\alpha^i] \tag{2.18}$$

where  $\alpha^i \in GF(q)$  are the symbols of the Galois field. The permutation process is depicted in Fig. 2.3 in the previous section.

## 4 - Check nodes processing:

After the multiplication with the non-binary elements of the PCM, all the parity nodes have the same behaviour and they become independant of the non-binary values of the parity check matrix. Each check node then computes the probabilities of the symbols that verify the parity conditioned to the input messages of that check node. The check update process can be expressed as a convolution of the incoming messages [DF07].

$$V_{cp_k} = \frac{\overset{d_c-1}{\circledast}}{\underset{j=0, j \neq k}{\circledast}} U_{p_j c}$$

(2.19)

The convolution can be realised as:

$$V_{cp_{k}}[\alpha^{i}] = \sum_{\substack{\delta: \sum_{m=0}^{d_{c}-1} \beta_{m(x)}=0}} \delta \prod_{j=0, j \neq k}^{d_{c}-1} U_{p_{j}c}$$

(2.20)

with  $v = \{0, 1, ..., d_c - 1\}$ ,  $\alpha^i \in GF(q)$ ,  $\beta_m$  represent the symbols that take part in the parity and  $\delta \in \{0, 1\}$  depending on whether the parity equation is verified.

Figure 2.7: The degree  $d_c = 3$  check node update

Fig. 2.7 depicts a check node of degree  $d_c = 3$ . The check node update eq. (2.20) can be explained as: The message value  $V_{cp_2}[\alpha^i]$  is calculated as a sum of all the products,  $U_{p_0c}[\alpha^j]U_{p_1c}[\alpha^k]$ , that verify the condition  $\alpha^j \otimes \alpha^k \otimes \alpha^i = 0$  with  $\alpha^j, \alpha^k, \alpha^i \in GF(q)$ and  $\otimes$  represents multiplication in the field.

#### **5** - Reverse-permutation processing:

After the messages have been updated at the check nodes, they are permuted back in the reverse direction at the permutation nodes. The value  $h_p^{-1}$  is used for the reverse permutation. It is realised by using eq. 2.40 in the reverse direction.

$$U_{pv}[\alpha^i] = U_{cp}[h_p \otimes \alpha^i] \tag{2.21}$$

## 6 - APP Calculation and the codeword decision:

Finally, the a-posteriori probabilities (APP) of the symbols are calculated at the variables using the new probabilities. A decision is then made on each symbol based on the highest APP.

$$\hat{v}_n = \max_{\alpha^i \in GF(q)} P_{ch}[\alpha^i] \prod_{j=0, j \neq k}^{d_v - 1} V_{p_j v}[\alpha^i] \quad , \quad \alpha^i \in GF(q)$$

(2.22)

The steps 2-6 are iteratively repeated until a valid codeword has been obtained or a fixed number of iterations has been completed. For a valid codeword to be obtained, the decoded codeword  $\hat{v}$  must satisfy  $H\hat{v} = 0$ , where H is the parity check matrix. If the maximum number of iterations are completed without decoding a valid codeword, a decoding failure is declared.

The main obstacle in the path of the hardware implementation of the BP decoding algorithm is its computational complexity, the major factor being the check nodes processing, which is composed of a high number of additions and multiplications. The decoding complexity of a GF(q) non-binary decoder is of the order  $\mathcal{O}(q^2)$ . Table 2.3 presents the no. of computations for a variable and check node of degrees  $d_v$  and  $d_c$  respectively. The nodes are processed with a recursive strategy called as the forward-backward (F/B) strategy [HDYW06], which is detailed in the next section.

Moreover, the normalization of the messages at the check nodes output, eq. 2.15, requires q divisions. As a consequence of the complexity, the hardware implementation for codes defined in order q > 16 can not be realised. Therfore, we directed our research towards proposing low complexity non-binary LDPC decoders and present our work in chapter-3 and chapter-4.

| Process            | Additions (+)   | Multiplications(×) | Division (÷) |

|--------------------|-----------------|--------------------|--------------|

| BP variable update | $d_v q$         | $(2d_v - 1)q$      | -            |

| BP check update    | $3(d_c - 2)q^2$ | $3(d_c - 2)q^2$    | q            |

Table 2.3: Computational complexity of the BP algorithm

## Binary LDPC codes vs. Non-binary LDPC codes

Binary LDPC codes have been extensively studied in literature and have been shown to approach the shannon limit performance for long length codes [RU01, CFRU01, LMSS01]. A lot of research has been carried out in finding ways to improve not only their decoding performance but also their structure which is better adapted to the transmission channel. In [RSU01], the authors proposed a method which allows us to predict the performance of binary LDPC codes in terms of probability of error. The proposed method is called as *density evolution* and it follows the evolution of the probability densities along with the propagated messages in the graph. However, it is difficult to analyse and predict the performance of NB-LDPC codes because the methods proposed for binary LDPC codes cannot be directly generalized to the non-binary case. Though, some authors have tried to generalize the methods based on density evolution for binary LDPC codes in order to optimise the construction of irregular NB-LDPC codes [LFK03, BB06, BT05, RU05]. However, the obtained profiles are not very accurate and could only be applied to very long codes. The difficulty is that the messages of a non-binary BP decoder are defined in high dimensional spaces, and it is in general difficult to keep track of their densities.

It is well known that the loss in performance of the BP algorithm comes from the inter-dependance of the messages flowing in the Tanner graph [YHB04]. The interdependance is created by specific topological structures that exist e.g. cycles, stopping and trapping sets. The reason is that the belief propagation algorithm is based on the application of Bayes rules locally at each check node, after which the a-posteriori probabilities are calculated for each variable node. In [KFL01], it was proved that for a cycle free graph, the local Bayesian function can be factorized to the a-posteriori probabilities of the symbols. In the cycle free case, all the messages are independant from each other, however, the presence of cycles bring along dependance between the messages which impairs the calculation of the exact a-posteriori probabilities. This determines that the BP algorithm is an optimal algorithm in the cycle free case and becomes sub-optimal with the introduction of cycles in the graph. The performance of the BP decoder is further decreased when the decoder is initialized with messages which have already been inter-correlated by the channel [Voi07].

Figure 2.8: Binary vs non-binary LDPC codes,  $N_b = 3008$  bits and R = 1/2

Figure 2.9: Binary vs non-binary LDPC codes,  $N_b = 565$  bits and R = 2/3

NB-LDPC codes [DM98] have shown better performance as compared to their binary counterparts, specially for higher order Galois fields [SF02, DCG04, BB06, MWZ06] and for codes of smaller length [MD99, SZAG06, ZLT<sup>+</sup>08]. This is mainly because the graph of a NB-LDPC code is more sparse as compared to their homologous binary counterparts for the same rate and binary code length [HFE04, PFD06a]. As a

result, we have a graph associated to NB-LDPC codes with better properties in terms of the number of cycles and their minimum length. Hence, a NB-LDPC code helps in avoiding short length cycles and thus improves the performane of the BP algorithm by avoiding the correlation induced in the messages due to the topological structures. The shortest cycle in a graph is called its girth. The girth of an irregular binary code of length  $N_b = 848$  bits and rate R = 0.5 has typically a girth equal to  $g_b = 6$  whereas a NB-LDPC code of the same length and rate has a girth  $g_{nb} = 14$ , provided that we have well constructed codes [DCG04, VP08, BB06].

Figure 2.10: Performance of regular GF(256) LDPC codes over a 16-QAM channel at a BER of  $10^{-5}$

It was also demonstrated that NB-LDPC codes have a better performance for channels with high spectral efficiency i.e. while using high order modulation [PML<sup>+</sup>09, BB06, DCG04, MD99]. For the case of a M - QAM modulated transmission while using binary LDPC codes, the MAP demapper at the receiver side constructs symbol like-lihoods which are inter-correlated at the binary level. This means that the decoder is initialized with already correlated messages even in the absence of cycles in the decoding graph. However, if the code is constructed in a non-binary Galois field with order greater than or equal to the modulation order, the decoder is initialized with uncorrelated messages which in turn improves the performance of the BP decoder. This was proved analytically and by means of simulations in [SF02].

Binary LDPC codes have shown good performance in the presence of burst errors [Tan81, WS98, YR01, PNF04]. However, NB-LDPC have shown even better performance in the presence of burst errors [MSV08, CWL05, LZL<sup>+</sup>07]. This is because

Figure 2.11: Performance of regular GF(256) LDPC codes over a 256-QAM channel at a BER of  $10^{-5}$

consecutive bits are grouped together forming symbols in the non-binary field GF(q). Moreover, NB-LDPC codes are being used in MIMO systems where they have shown better performance [JYgXL09, BF04] as compared to binary LDPC codes. It exhibits a better balance between performance and complexity when detection and decoding are performed jointly as compared to when done separately[PC06].

The main reason to use NB-LDPC codes in place of binary LDPC codes lies in the fact that for a finite length code, while using a sub-optimal low complexity algorithm, NB-LDPC decoders have a performance very close to the maximum-likelihood decoder (MLD) as compared to binary LDPC decoders [Voi07]. We now present the comparison of the error correcting performance of binary vs. non-binary LDPC codes.

Fig. 2.8 and 2.9 represent the performance comparison for short length codes transmitted over a binary-AWGN channel. The codes considered have the same rate and length. We see a gain in performance while using GF(64) as compared to the binary codes. Similarly, while using GF(256) codes, we also obtain a very low error floor.

We now present the performance comparison of NB-LDPC codes for high order modulations. The figures 2.10 and 2.11 represent the values of the  $E_b/N_o$  for which the frame error rate (FER) is  $10^{-5}$  for different ultra-sparse ( $d_v = 2$ ) NB-LDPC codes defined over GF(256). The codeword lengths considered were N = 2000, 8000 and 40000 bits. We can observe Fig. 2.10, that for N = 40000, there is a loss of 0.5dB as compared to the channel capacity for 16-QAM modulation. However, for 256-QAM modulation in Fig. 2.11, the loss in performance from the channel capacity is increased to 1.2dB. The same behaviour is observed for N = 8000 and 2000 as well. This shows that using an order of field higher than the modulation order results in better performance.

Therefore, NB-LDPC codes are considered as the candidates for future communication systems.

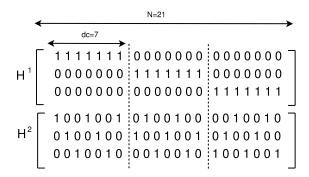

## 2.1.2 NB-LDPC codes defined on general linear groups

In this section, we detail another class of low density parity check codes defined over finite linear groups  $\mathbb{G}(q)$ , which is a more general framework as compared to LDPC codes defined over finite Galois fields GF(q). This allows us to consider a wider class of LDPC codes as compared to codes defined in a finite Galois field [SD06].

## Parity check constraints defined over groups

Let  $\mathbf{c} = [c_0...c_{N-1}]$  be a codeword of an LDPC code defined over a finite Galois field GF(q), with  $q \ge 2$ . The *i*<sup>th</sup>-parity equation is written as:

$$\sum_{j:h_{ij}\neq 0} h_{ij}c_j \stackrel{GF(q)}{=} 0 \tag{2.23}$$